2-D parity checkup correction method and its realization hardware based on advanced encryption standard

An advanced encryption standard and parity check technology, which is applied in the field of concurrent error detection method based on two-dimensional even check and its hardware implementation, which can solve the problem that even number of errors cannot be reached, the error coverage rate is low, and the hardware security of the advanced encryption standard is affected. Sex and other issues, to achieve the effect of resisting error attacks

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

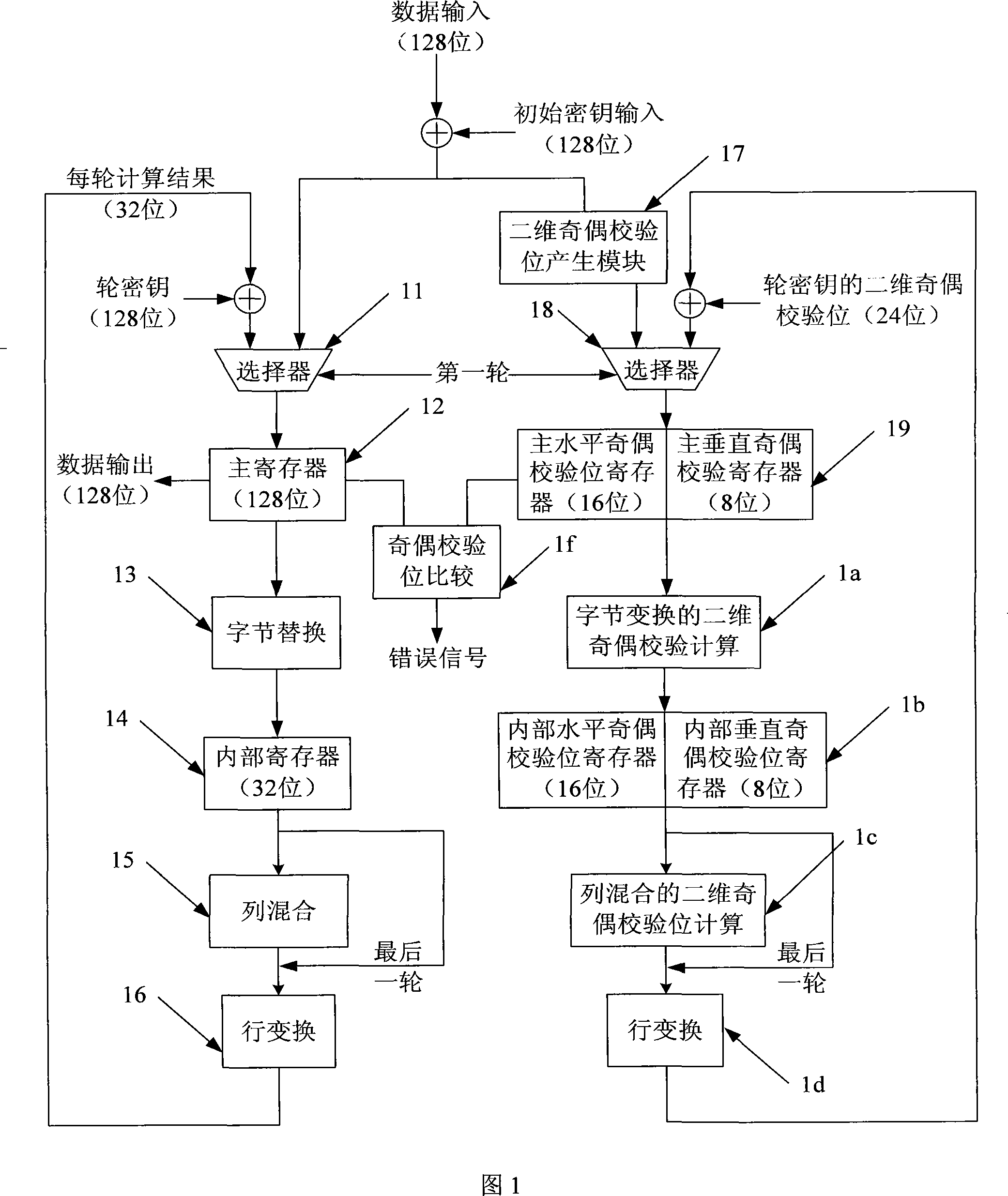

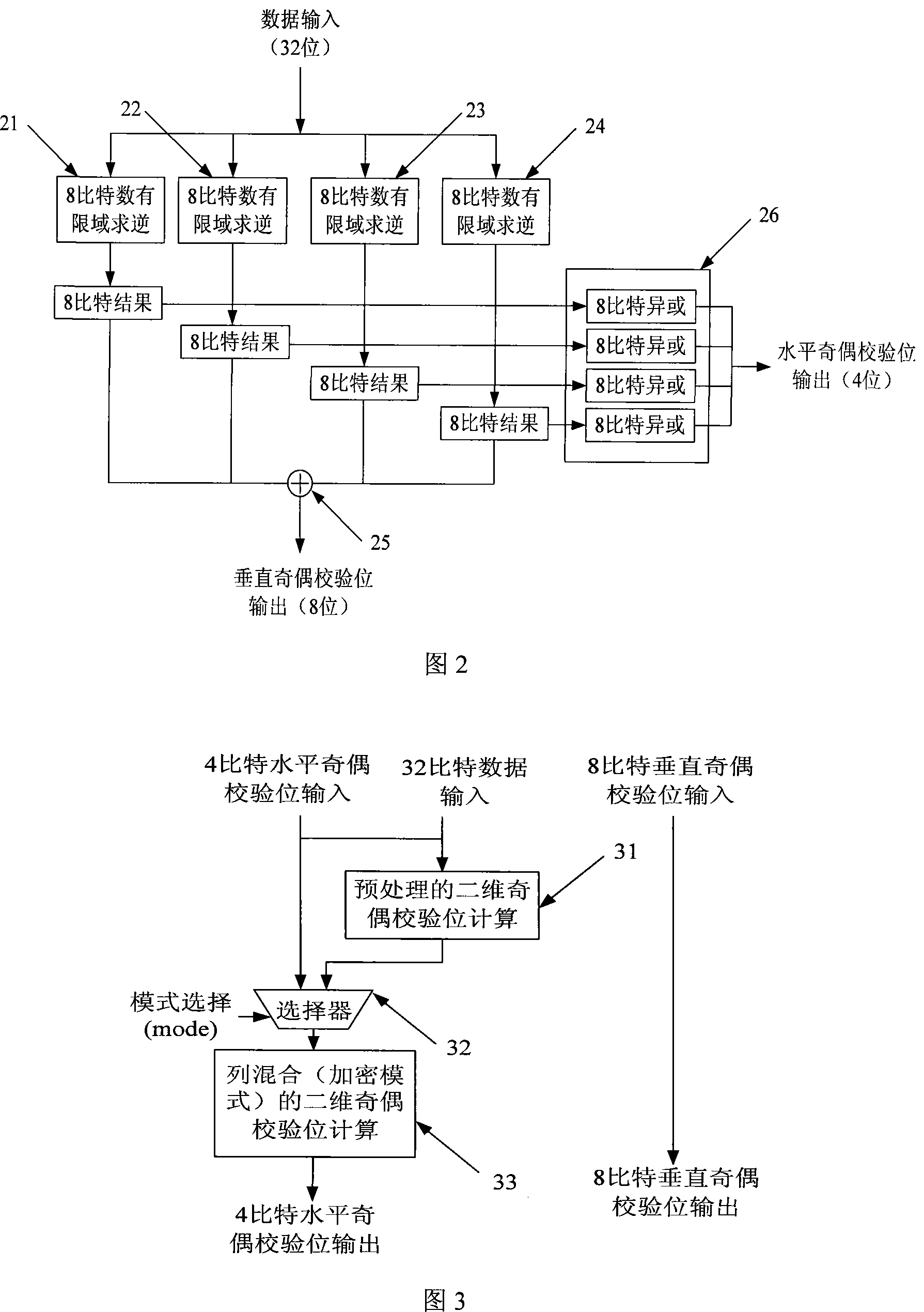

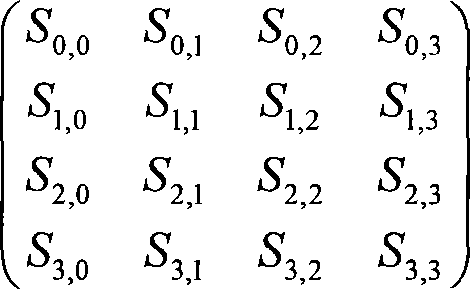

[0079] The invention proposes an advanced encryption standard anti-differential error attack-based concurrency error detection method based on two-dimensional parity check, which includes the calculation of parity bits in the horizontal direction and the vertical direction. Its hardware implementation structure divides the 128-bit Advanced Encryption Standard operation into four groups of 32-bit data. The concurrency error detection method proposed by the present invention and its hardware implementation structure will be described in detail below in conjunction with the diagrams.

[0080] The present invention is aimed at the Advanced Encryption Standard with a data and key length of 128 bits, as shown in Formula 1. In the Advanced Encryption Standard, the data and the key are all 16 bytes, so the two-dimensional parity check method proposed by the present invention can calculate the parity bit in the horizontal direction and the vertical direction, and the specific calculati...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com