Layering placement modeling method for modern programmable logic device software system

A technology of software system and modeling method, which is applied in the electronic field and can solve problems such as unusable

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

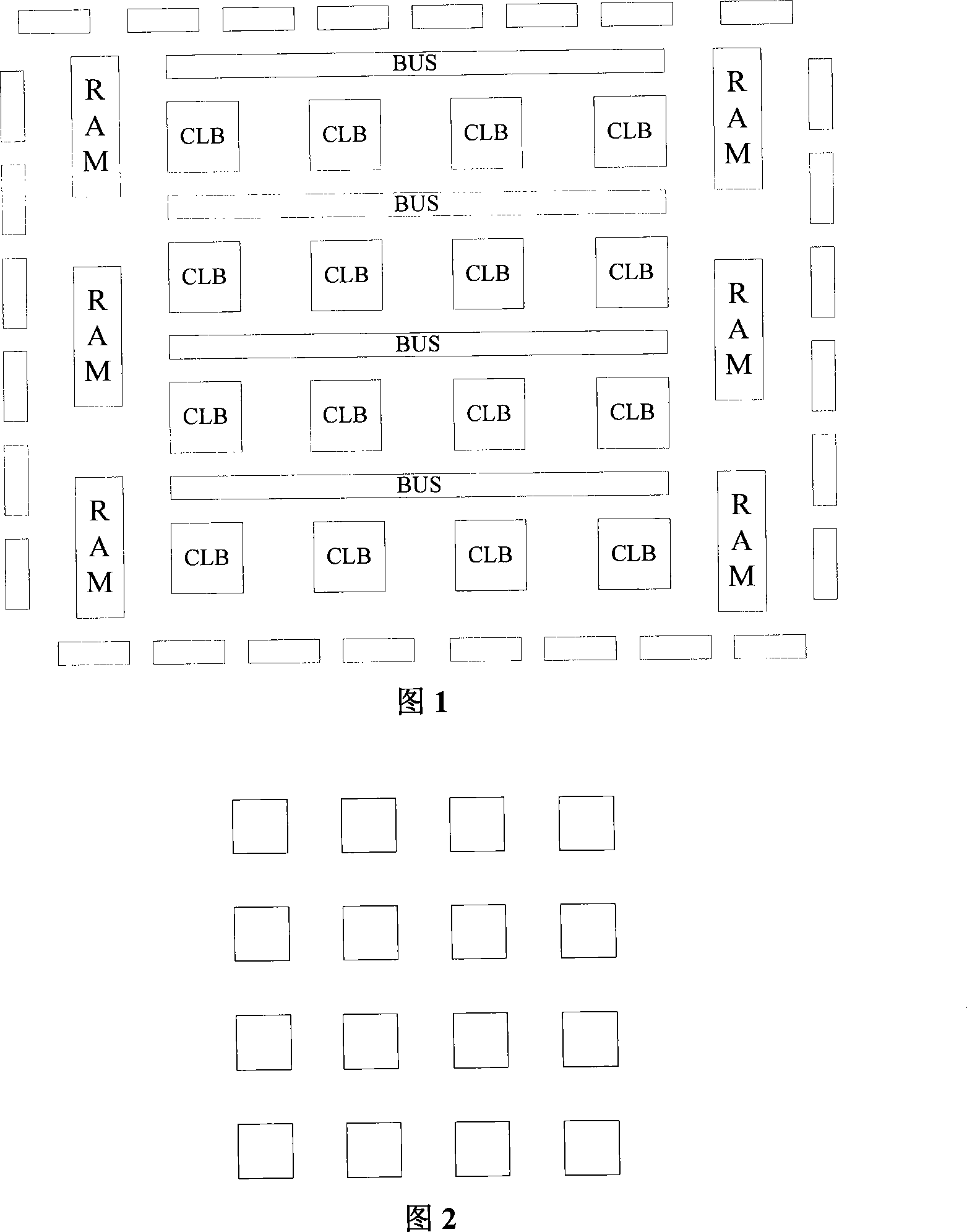

[0023] Taking the SpartanII chip of Xilinx Company as an example, its chip structure is shown in Figure 1. The chip has a total of programmable logic block (SLICE), programmable input and output block (IOB), bus (TBUF), block random access memory (RAM) and other module types. The programmable logic block (SLICE) is evenly distributed within the chip area; the bus (TBUF) is distributed between each row of programmable logic blocks (SLICE); the block random access memory (RAM) is distributed on the left and right sides of the chip area; programmable Input-output blocks (IOBs) are distributed around the chip area.

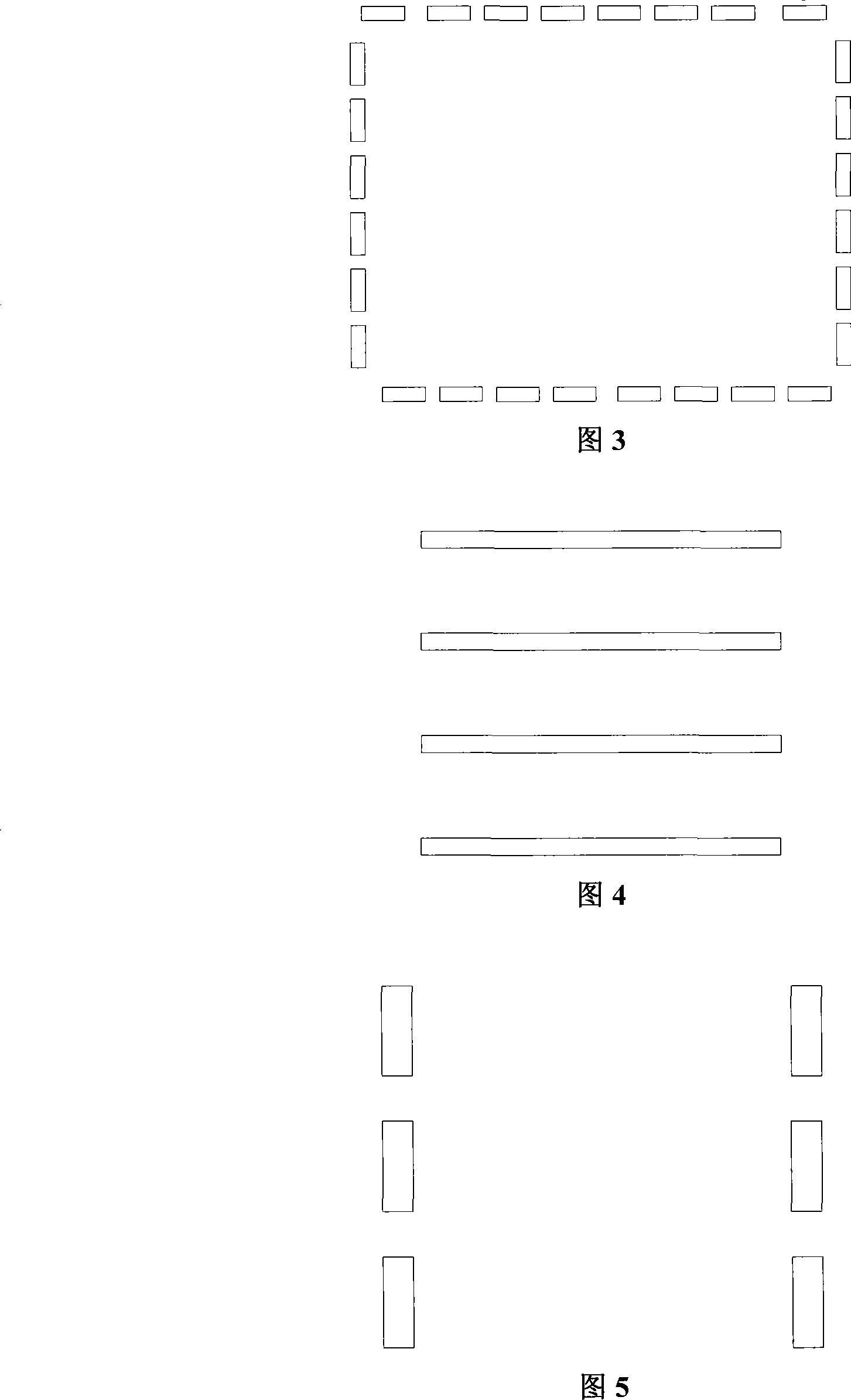

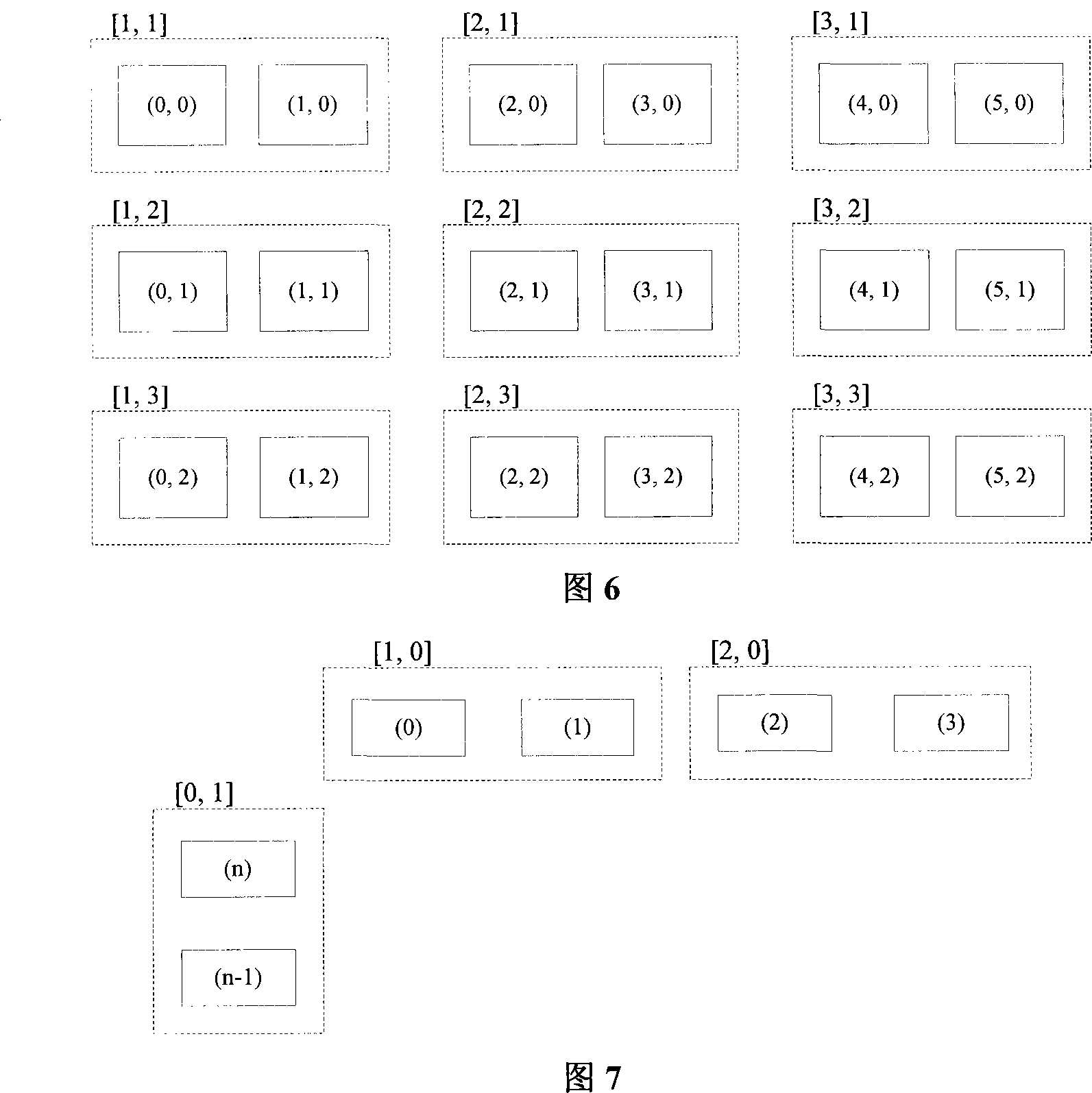

[0024] All logic units of the same type on the FPGA chip form a logic unit layer. The structure of the programmable logic block (SLICE) layer is shown in Figure 2; the structure of the programmable input-output block (IOB) layer is shown in Figure 3; the structure of the bus (TBUF) logic layer is shown in Figure 4; block random access memory (RAM) The structure of t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com