Firewall chip data packet buffer management method

A cache management and data packet technology, applied in data exchange networks, digital transmission systems, electrical components, etc., can solve the problems of occupying a lot of memory, long data packet processing time, low efficiency, etc., so as to reduce moving and improve memory usage. , the effect of reducing complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

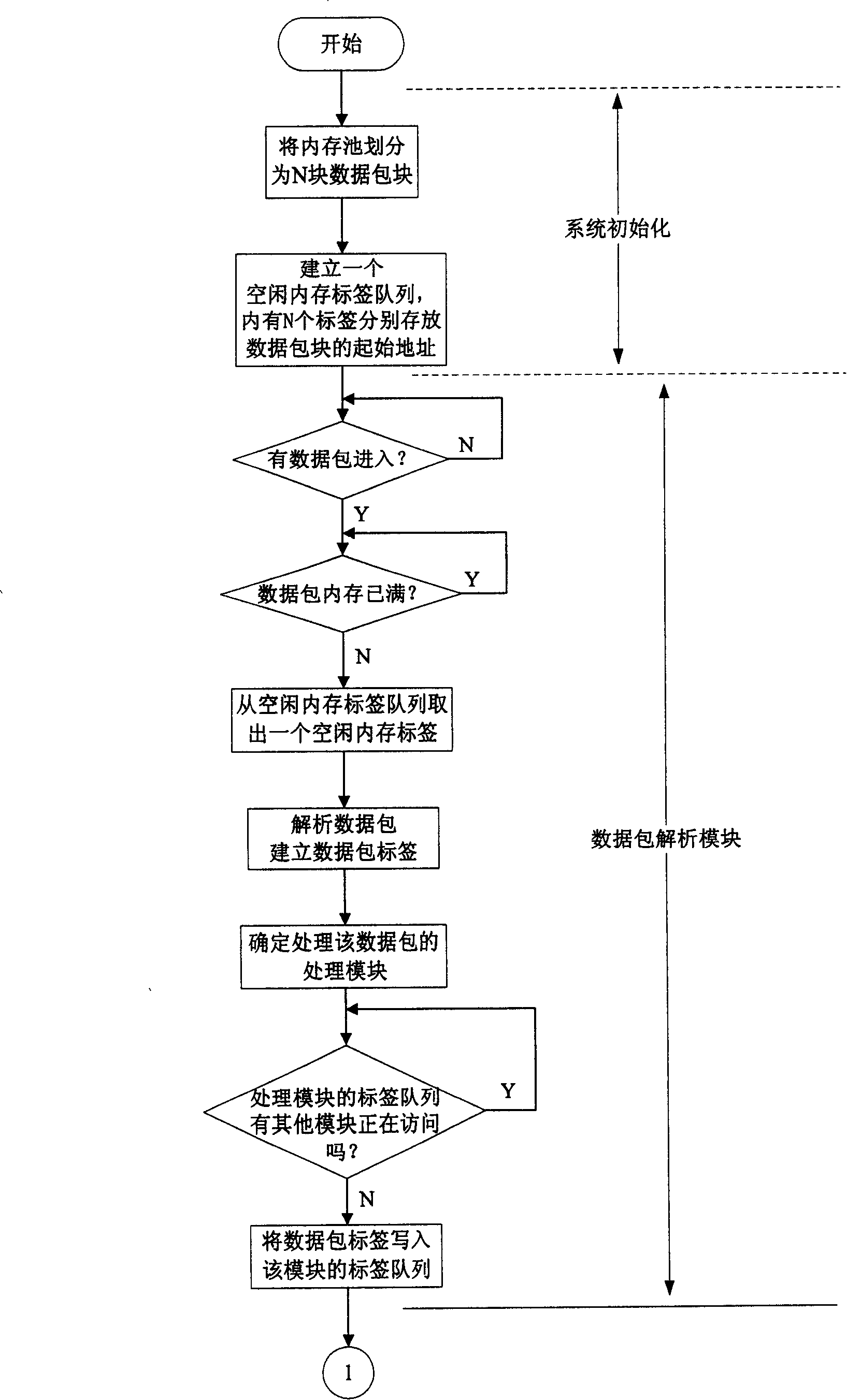

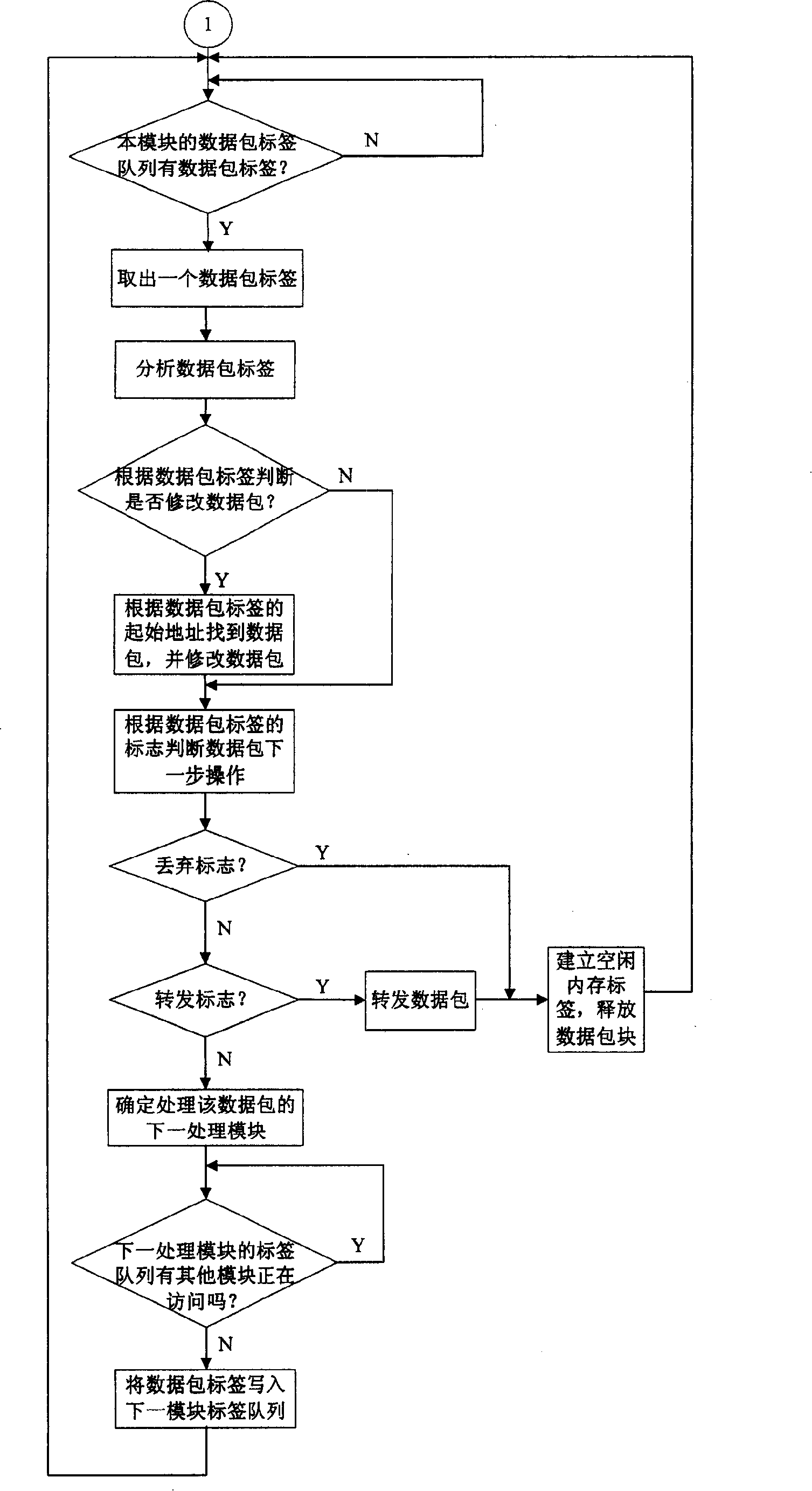

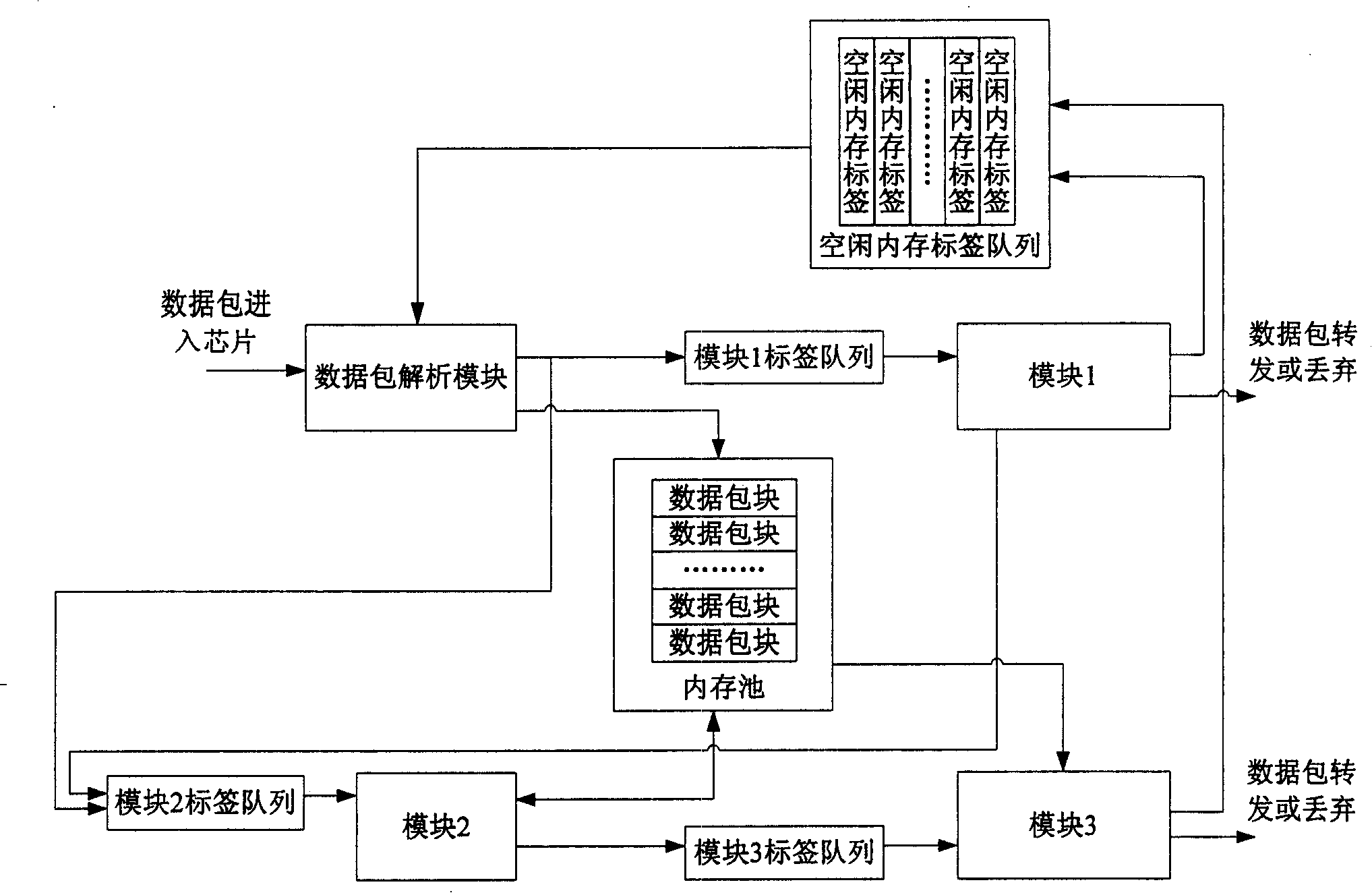

[0032] The specific implementation of the present invention will be further described below in conjunction with accompanying drawing:

[0033] The invention proposes a method for the firewall chip to manage the internal data cache and the external data cache through the internal label queue, so as to improve the memory usage efficiency. The overall technical solution is: first step, initialize the memory pool, and establish a free memory label; second step, allocate memory for each data packet, corresponding to a free memory label, extract the characteristics of the data packet at the same time, establish a data packet label, and Each processing module transmits and modifies the data packet label; the third step is to discard or forward the data packet according to the data packet label containing the processing results of each module, and then release the memory occupied by the data packet.

[0034] Such as figure 1 , figure 2 Shown, the present invention comprises followi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com