RISC processor device and multi-mode data processing method

A data processing and processor technology, applied in the field of computer microprocessors, can solve problems such as reducing processor performance, achieve the effects of increasing computing speed, saving translation time, and improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

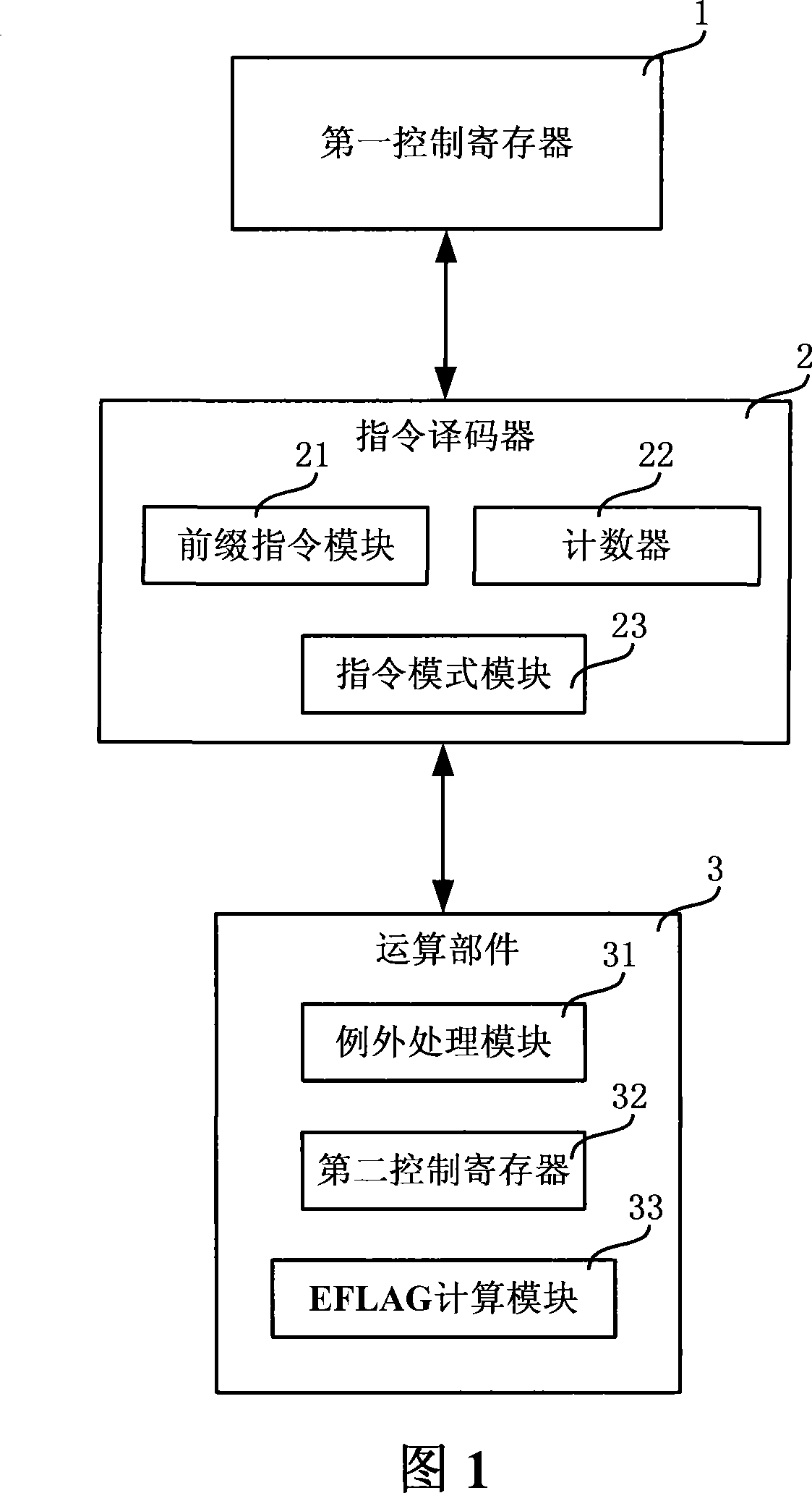

[0068] As an implementable mode, the judging module of the RISC processor device of the present invention is a first control register 1, and the first control register 1 includes a control bit flag X86MODE1, and when this bit is 1, it means that at this time The corresponding instruction runs in the X86 virtual machine instruction set mode; when the flag is 0, it means that the corresponding instruction runs in the non-X86 virtual machine instruction set mode at this time.

[0069] In the MIPS64 instruction set of the RISC processor, some Coprocessor0 (CP0) control registers are reserved for user-defined. For example, register No. 22 is reserved for user-defined in the case of all Sel bits.

[0070] Embodiments of the present invention utilize one of these control registers (CP0) as the X86 mode control flag X86MODE1. When it is necessary to distinguish the mode of the instruction, it can be judged by reading the corresponding bit of the control register. When the flag bit is ...

Embodiment 2

[0075] As an implementable mode, in the RISC processor device of the present invention, the judgment module is a prefix instruction module 21 included in the instruction decoder 2, and the prefix instruction module 21 includes a prefix instruction X86MODE2 for Indicates that multiple instructions following the instruction are in the X86 virtual machine instruction set mode.

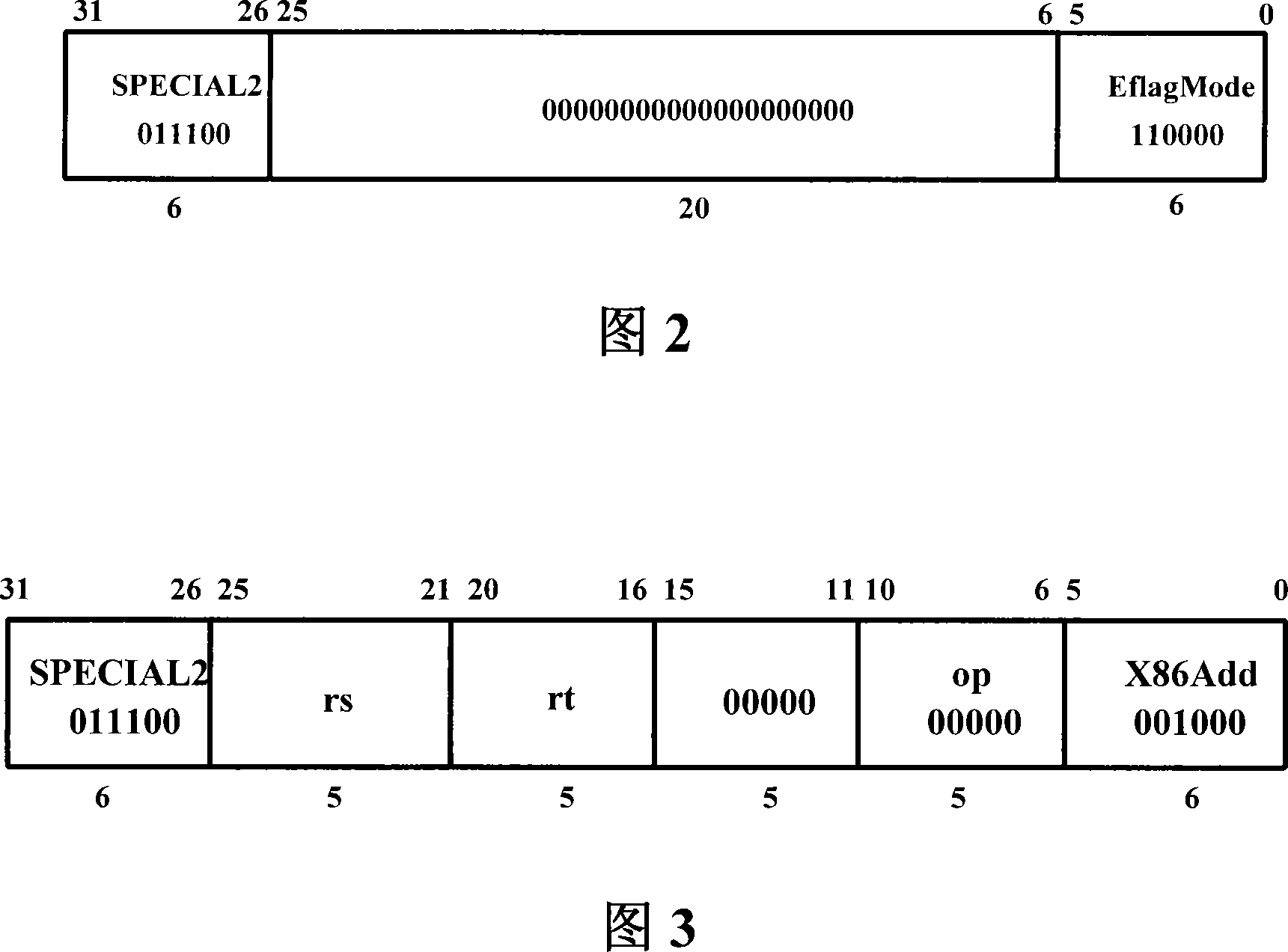

[0076] For the prefix instruction in the prefix instruction module 21 of the embodiment of the present invention, the format in the MIPS64 instruction set of the RISC processor is as follows figure 2 As shown, it is implemented using the reserved value of the empty slot of SPECIAL2 in the MIPS instruction set.

[0077] The prefix instruction module 21 of the instruction decoder 2 sets a flag when decoding the prefix instruction, and the instruction behind this instruction is translated into the X86 virtual machine instruction set mode, and then the prefix instruction is translated into an empty operation...

Embodiment 3

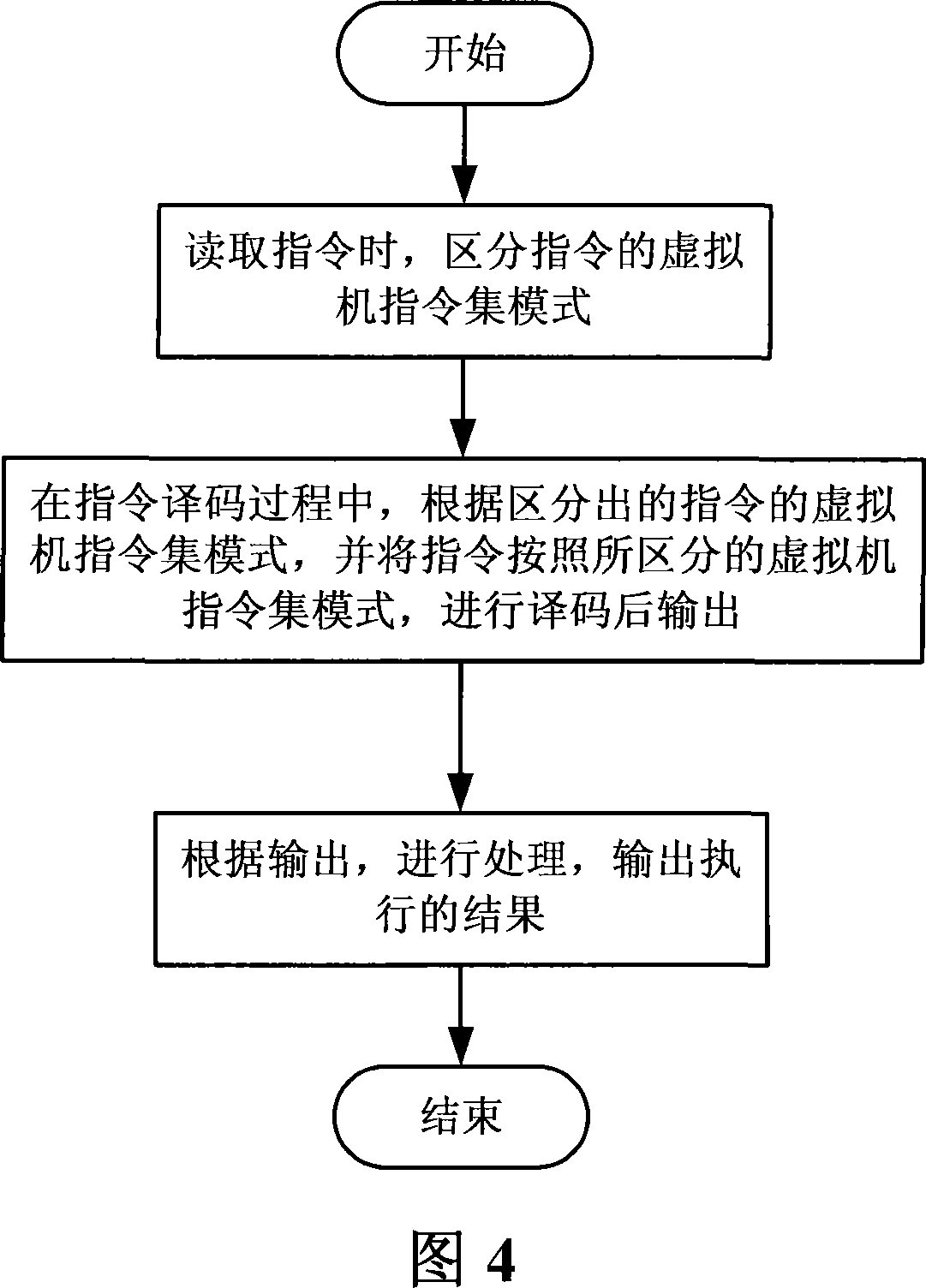

[0085] As another implementable manner, the judging module is an instruction mode module 23, configured to mark the virtual machine instruction set mode of the instruction in the MIPS instruction of the RISC processor.

[0086] For the X86 virtual machine instruction with high frequency of use, it is necessary to set a sign in the MIPS instruction set of the RISC processor through the instruction mode module 23, indicating that the MIPS instruction is an instruction executed under the X86 virtual machine instruction set mode . In this way, for frequently used X86 virtual machine instructions, the instruction is marked as the X86 virtual machine instruction set mode, and is directly executed by the MIPS instruction set of the RISC processor, so as to reduce the corresponding overhead.

[0087] The instructions affected by the instruction mode module 23 can only affect the decoding and execution of the instruction, and have no effect on other instructions, and other instructions...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com