Semiconductor chip cleaning system

A technology for cleaning systems and semiconductors, applied in the manufacture of semiconductor/solid-state devices, electrical components, circuits, etc., can solve the problems of easily damaged wafers, reduced wafer productivity, uneven clamping conditions of clamping fingers, etc., to achieve cleaning effects, Improved wafer productivity, optimum cleaning performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] Hereinafter, a semiconductor wafer cleaning system according to a preferred embodiment of the present invention will be described in more detail with reference to the accompanying drawings.

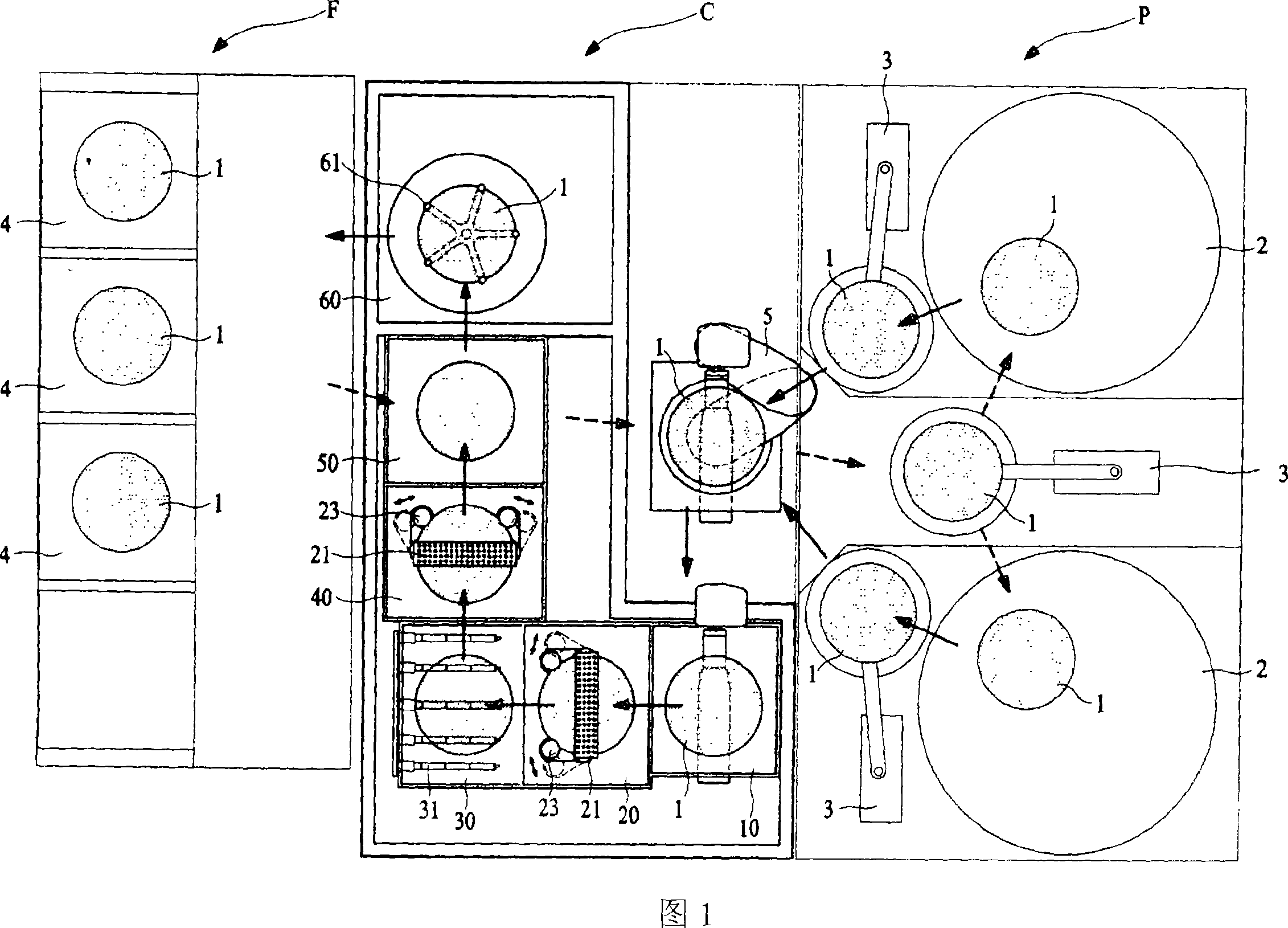

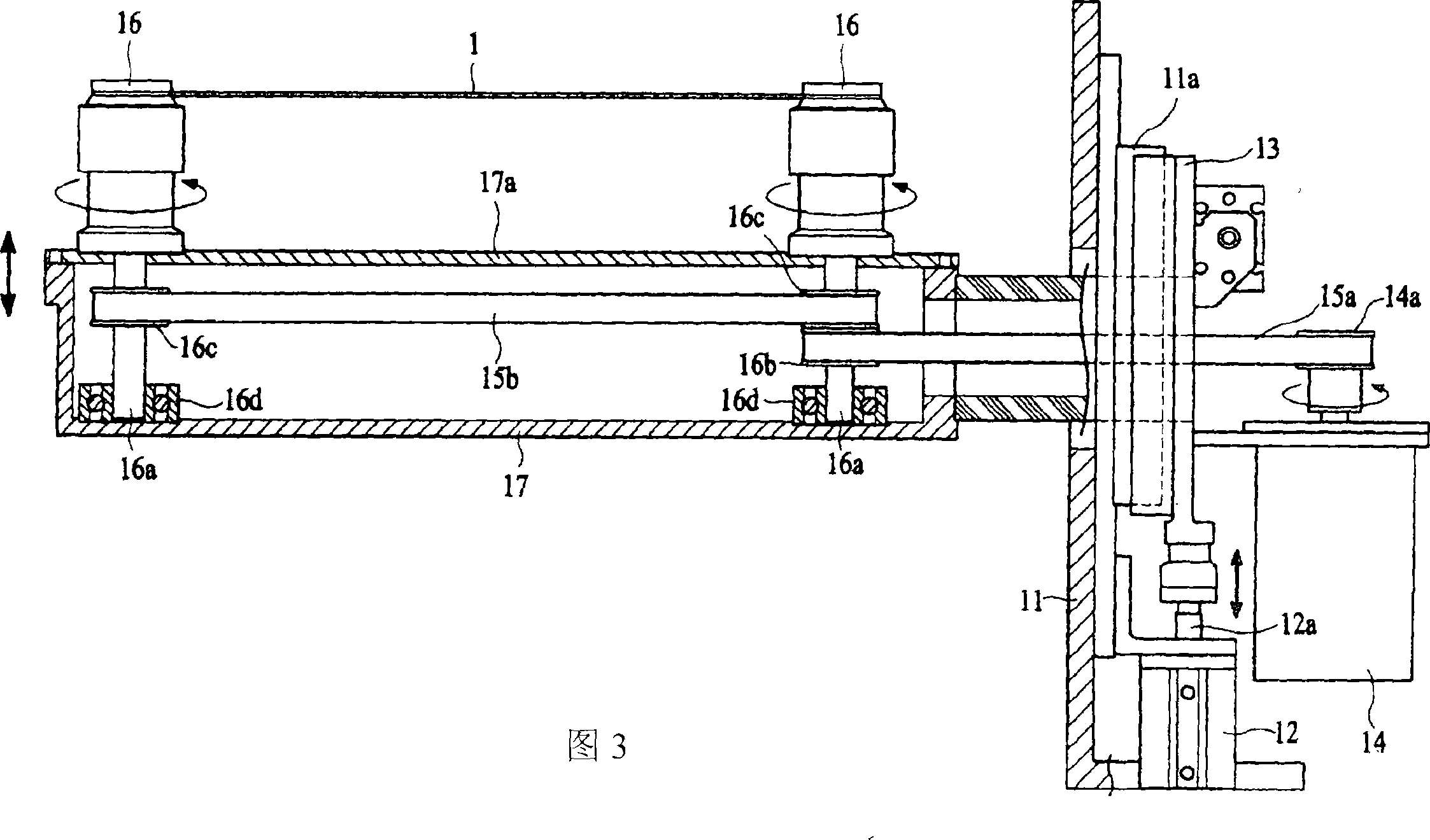

[0037] 1 to 11 are views explaining a semiconductor wafer cleaning system C according to the present invention. More specifically, Fig. 1 is a schematic diagram of the disposition structure of each part of the semiconductor wafer cleaning system C according to the present invention and its connection with peripheral devices such as a polishing module P and a wafer receiving module F in a plane; Fig. 2 is applied to A schematic diagram of the main structure of the pre-cleaning station 10 of the cleaning system C of the present invention, which is used to remove larger particles through the water curtain type injector 18 of deionized water; FIG. 3 is along the line shown in FIG. 2 Sectional view taken from III-III; Fig. 4 is a perspective view of the main structure of the first clean...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com