Method of fabricating recess channel in semiconductor device

A technology for semiconductors and devices, applied in the field of manufacturing semiconductor devices, can solve the problems of reducing reproducibility, defects in product characteristics, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

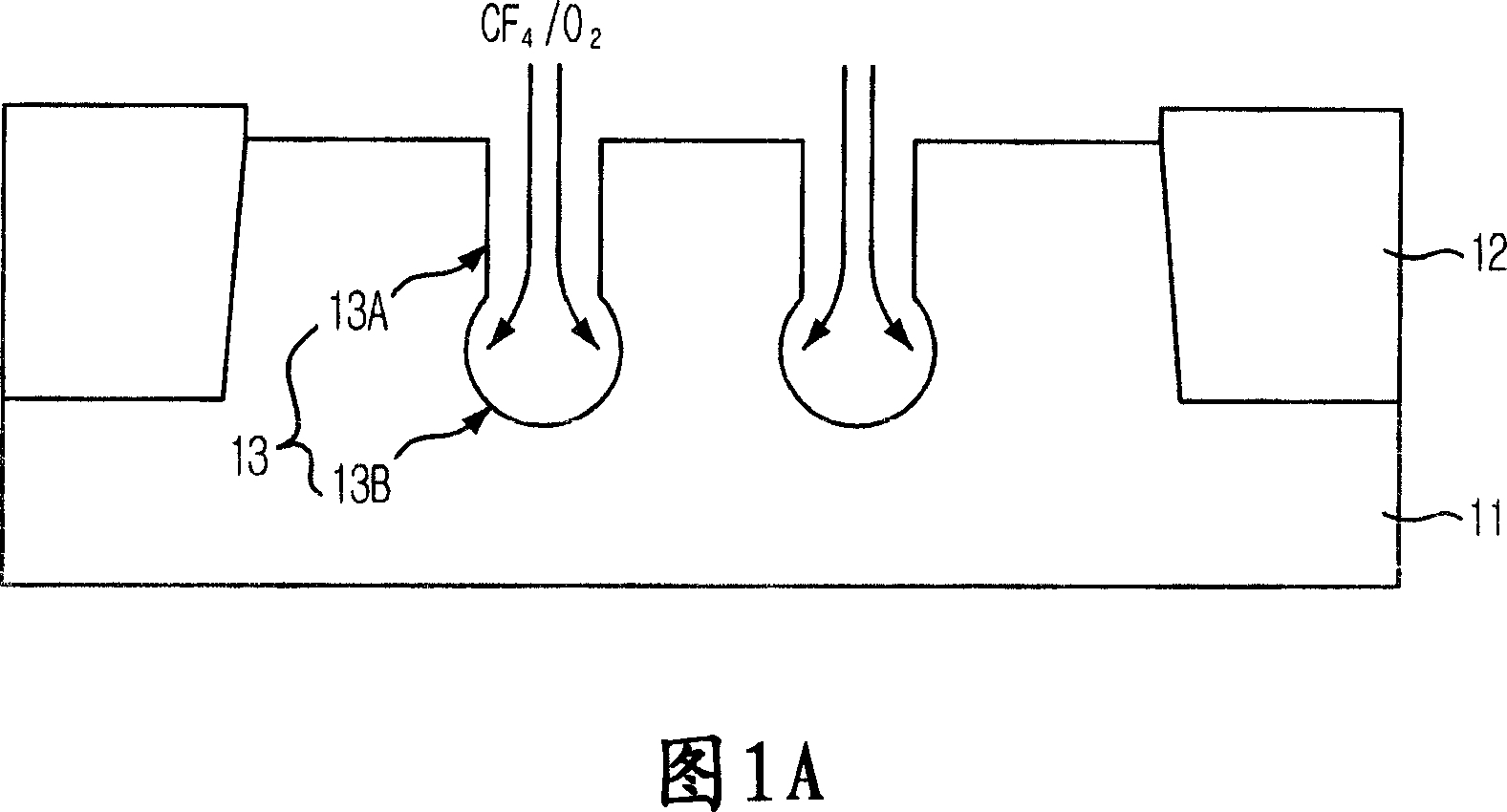

[0016] The present invention relates to a method of manufacturing a recessed channel with a highly reproducible ball pattern in a semiconductor device. When forming the recessed channel including the neck pattern and the ball pattern, the shape of the ball pattern can be precisely formed by controlling the etching process conditions for forming the ball pattern.

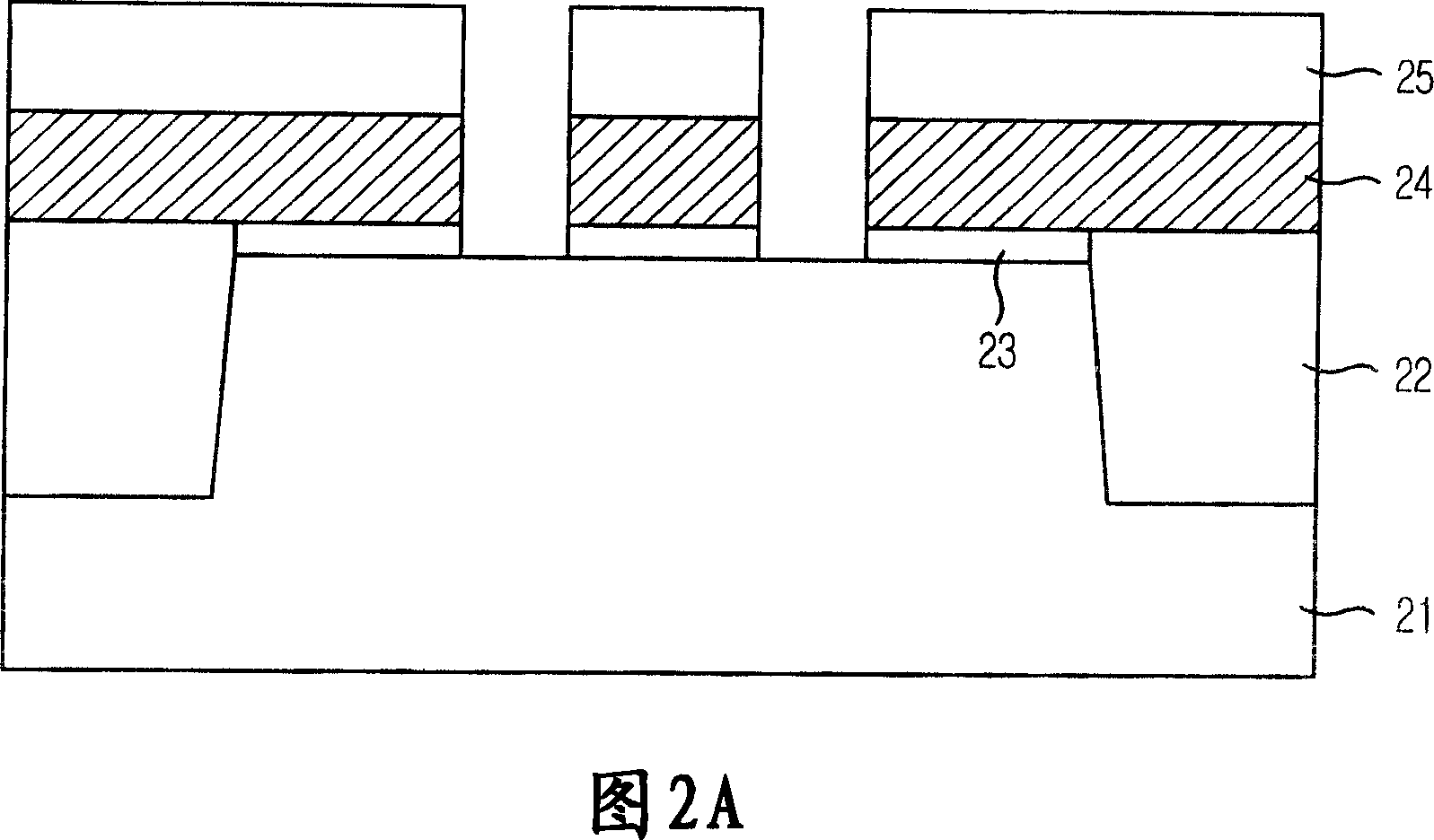

[0017] 2A-2F are schematic cross-sectional views of a method of making a recessed channel in accordance with certain embodiments of the present invention.

[0018] Referring to FIG. 2A , a device isolation structure 22 may be formed on a substrate 21 using a shallow trench isolation (STI) process. The device isolation structure 22 is filled in the trench. The trench has a depth of about 3000 Ȧ to about 4000 Ȧ.

[0019] As is well known, the STI process includes forming a pad oxide layer on the substrate 21 using a chemical vapor deposition (CVD) method. The pad oxide layer has a thickness of about 100 Ȧ to about 3...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com