Device and method for compensating MOS device grid leakage current

A gate leakage current, MOS device technology, applied in instruments, adjusting electrical variables, control/regulating systems, etc., to achieve the effects of reducing jitter, reducing circuit area, and improving working conditions

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0041] Please refer to FIG. 3 , which is a schematic structural diagram of a gate leakage current compensation device in an embodiment of the present invention, which mainly includes: a mirror circuit, a compensation current unit and a feedback control unit.

[0042] Among them, the mirror circuit is used to output the mirror voltage to the feedback control unit to generate the mirror current. The ratio of the gate leakage current of the compensated circuit to the mirror current is called the mirror ratio parameter. By setting the circuit of the compensated circuit and the mirror circuit The parameter can obtain the determined mirror ratio parameter; the structure of the mirror circuit corresponds to the circuit to be compensated to form its mirror image;

[0043] The compensation current unit is a unit that outputs a stable current under the control of the input control voltage, including two voltage-controlled current sources, one voltage-controlled current source is used to ...

Embodiment 2

[0055] Please refer to FIG. 4 , which is a specific embodiment of the present invention, which is a circuit diagram of a MOS device gate leakage current compensation device applied to a PLL circuit.

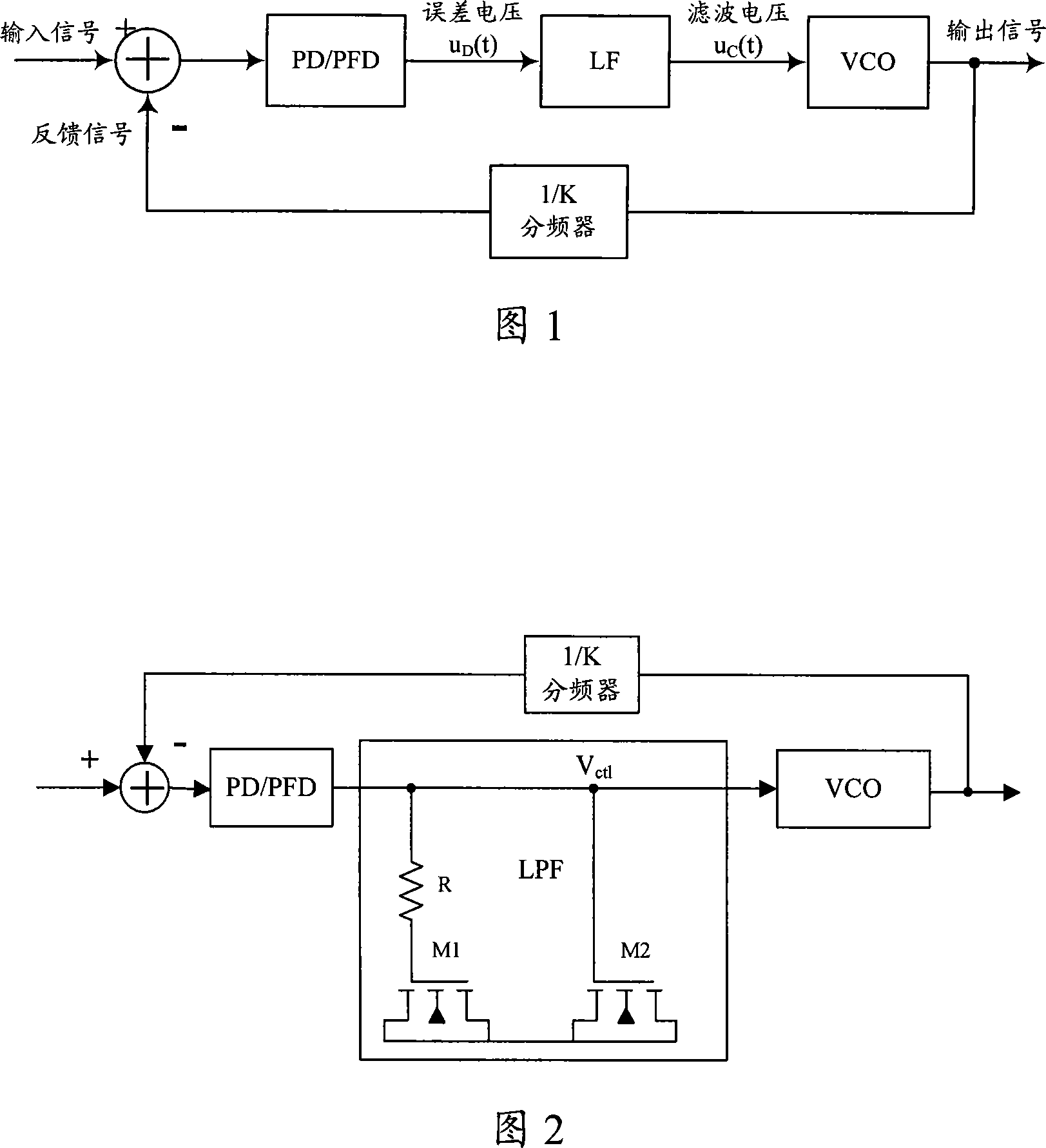

[0056] In the figure, PD or PFD, VCO, LPF and 1 / K frequency divider are all part of the conventional PLL circuit. The LPF is composed of a resistor R and NMOS transistors M1 and M2. M1 and M2 are thin gate MOS transistors with large capacitance per unit area. LPF output filter voltage V ctl is the VCO input voltage. Under deep sub-micron conditions, due to the tunneling effect, the MOS tube will generate a gate leakage current, which will affect the stability of the filter voltage in the PLL circuit and bring large jitter, which will seriously affect the PLL circuit. working status.

[0057] In this embodiment, the circuit to be compensated is the LPF, and a MOS device gate leakage current compensation circuit is added in the dotted line box to compensate the gate leakage curr...

Embodiment 3

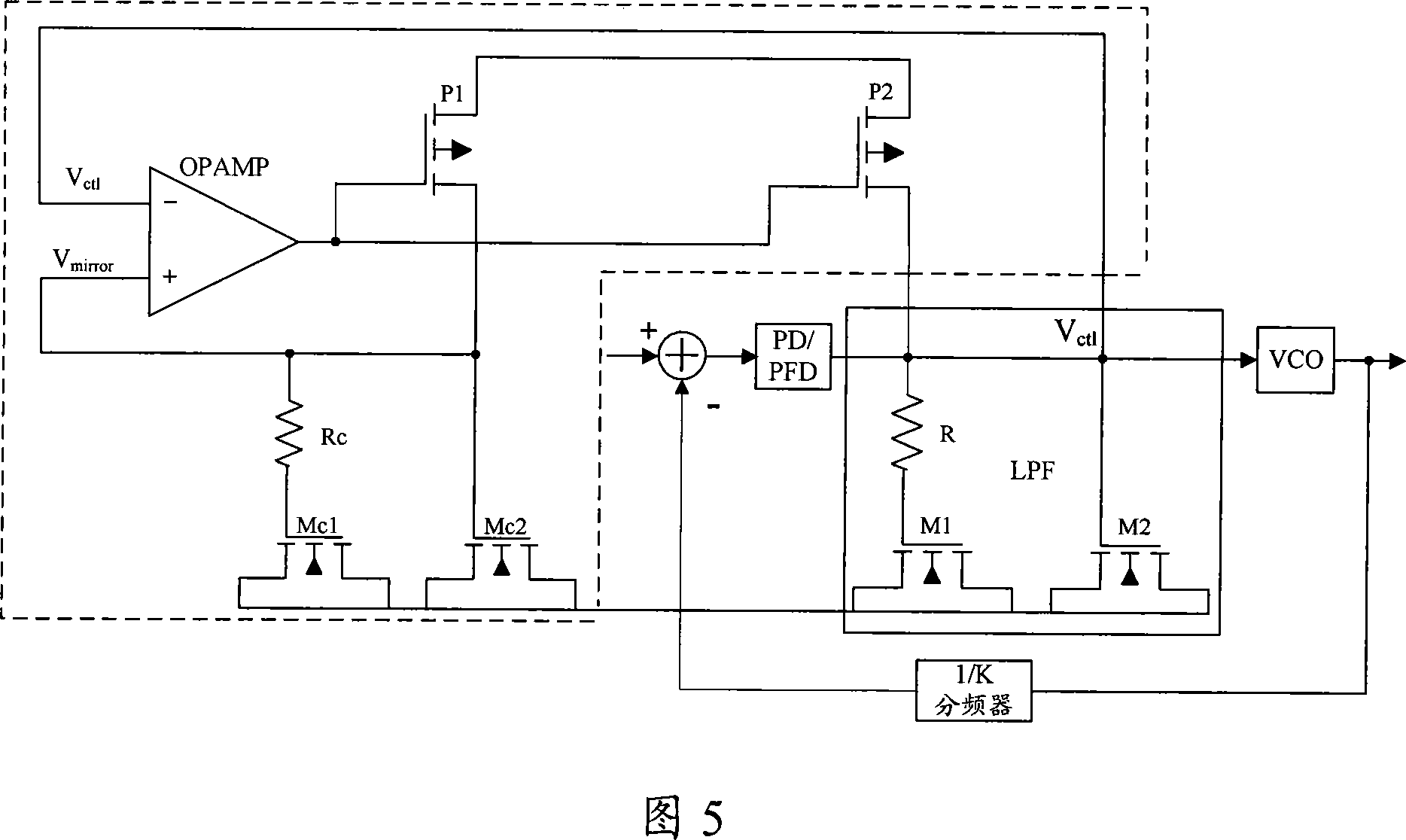

[0075] FIG. 5 shows another specific embodiment of the gate leakage current compensation circuit of the MOS device in the deep submicron PLL, which is a specific implementation of the second embodiment, wherein the feedback control unit is composed of an operational amplifier (Operational Amplifier, OPAMP) is implemented, and the voltage-controlled current source is implemented by a P-channel MOS (PMOS) tube. In this embodiment, the circuit to be compensated is an LPF, and the MOS device gate leakage current compensation circuit includes: a mirror circuit of the LPF, two PMOS transistors P1 and P2, and one OPAMP. The selection and connection methods of each device are described as follows:

[0076] The mirror circuit of LPF is composed of two NMOS transistors Mc1, Mc2 and a resistor Rc, the connection mode is corresponding to LPF; Mc1 is the mirror image of M1, the area is 1 / N of M1, and N is the mirror ratio parameter; Mc2 is the mirror image of M2 , the area is 1 / N of M2; R...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com