Semiconductor package substrate for improving deform

A technology for packaging substrates and semiconductors, applied in semiconductor devices, semiconductor/solid-state device parts, electric solid-state devices, etc., to achieve the effects of avoiding deformation, reducing the degree of subsidence and collapse, and preventing wrinkles or deformation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 Embodiment

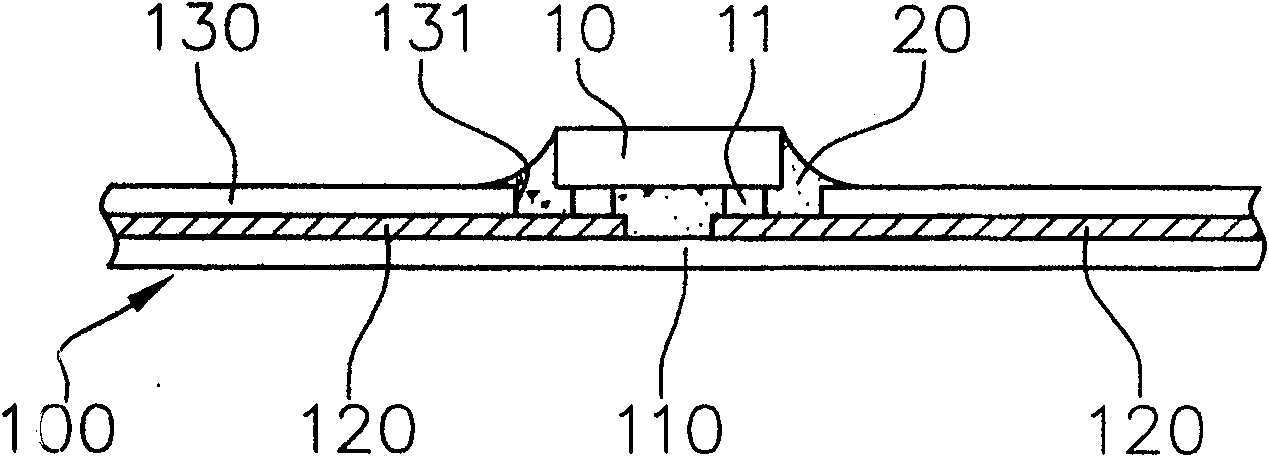

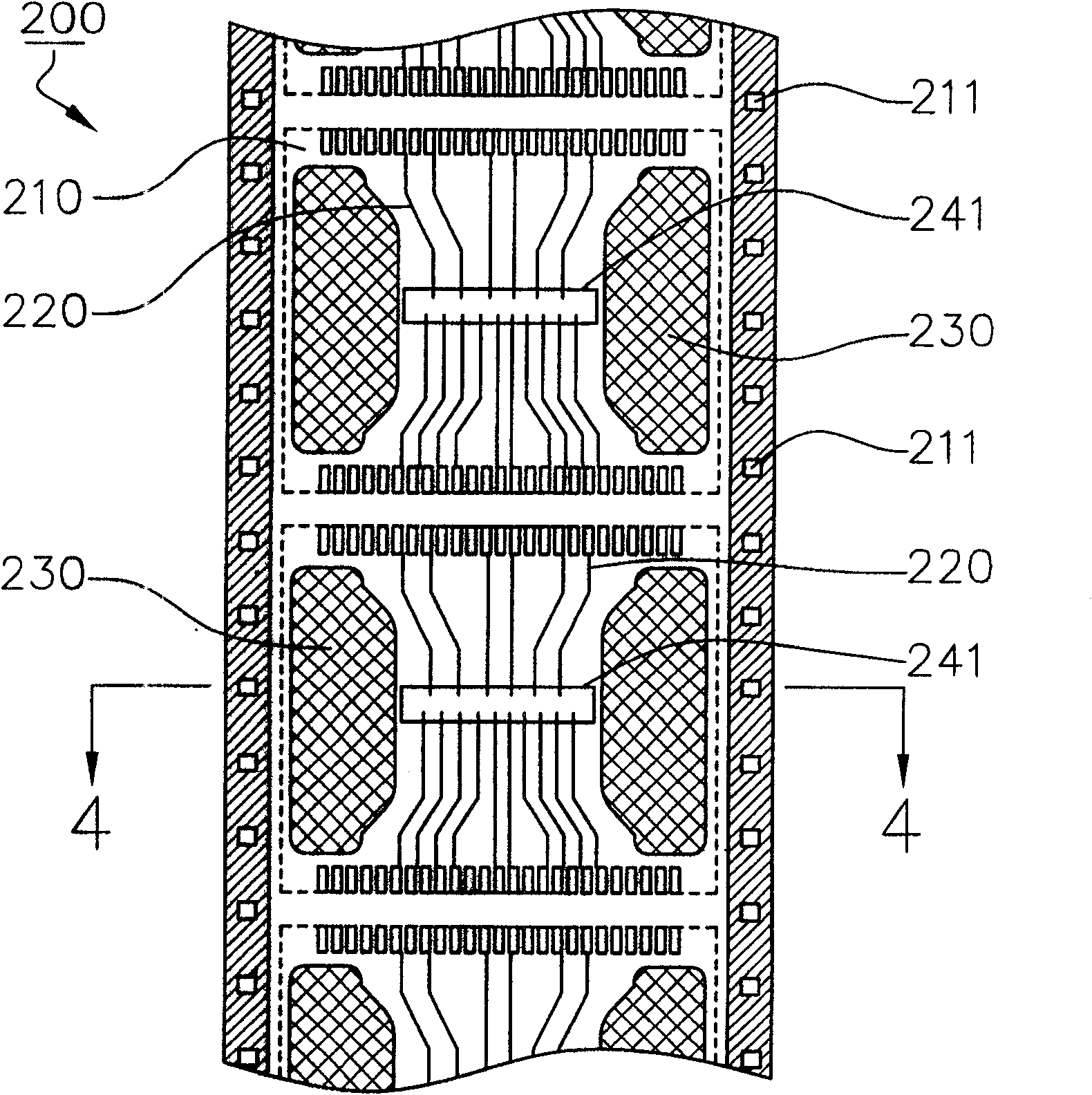

[0046] According to a first embodiment of the present invention, a semiconductor packaging substrate with improved deformation is disclosed. Such as image 3 and Figure 4 As shown, the semiconductor package substrate 200 mainly includes a flexible dielectric layer 210 , a plurality of pins 220 , at least one reinforcing metal pattern 230 and a solder resist layer 240 . The pins 220 and the reinforcing metal pattern 230 are formed on the same surface of the flexible dielectric layer 210 . The flexible dielectric layer 210 is an organic dielectric film layer, and usually the material of the flexible dielectric layer 210 can be polyimide (polyimide, PI) or polyester (PET), etc., as these lead The carrier film of the feet 220 and the reinforcing metal pattern 230 is particularly suitable for tape-and-roll transport for semiconductor packaging operations. The semiconductor package substrate 200 includes a plurality of carrier units corresponding to packaged products.

[0047]T...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com