Thin film SOI thick grid oxygen power device with grid field plate

A gate field plate and power device technology, applied to semiconductor devices, electrical components, circuits, etc., to achieve large gate-source voltage, reduce on-resistance, and reduce loss

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

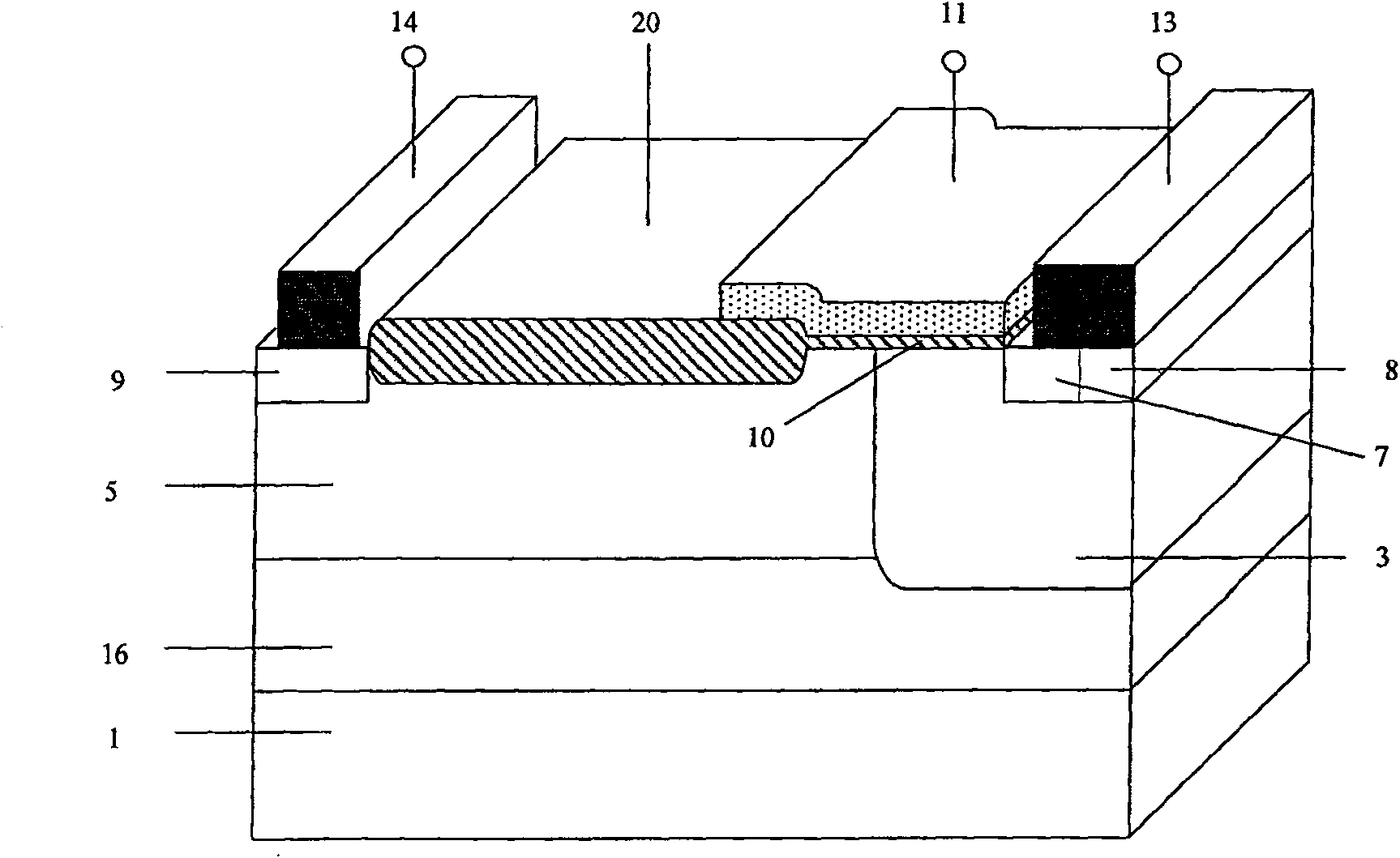

Image

Examples

Embodiment Construction

[0028] By adopting the thin film SOI novel thick gate oxide power device structure with gate field plate of the present invention, a power device with excellent performance of high voltage, high speed and low conduction loss can be obtained. In particular, the high-voltage thick gate oxide device that can realize 60V to 300V meets the withstand voltage requirements of the high-voltage PMOS for the level shift circuit in the 70-100V PDP address driver IC and the 170-275V PDP row driver IC.

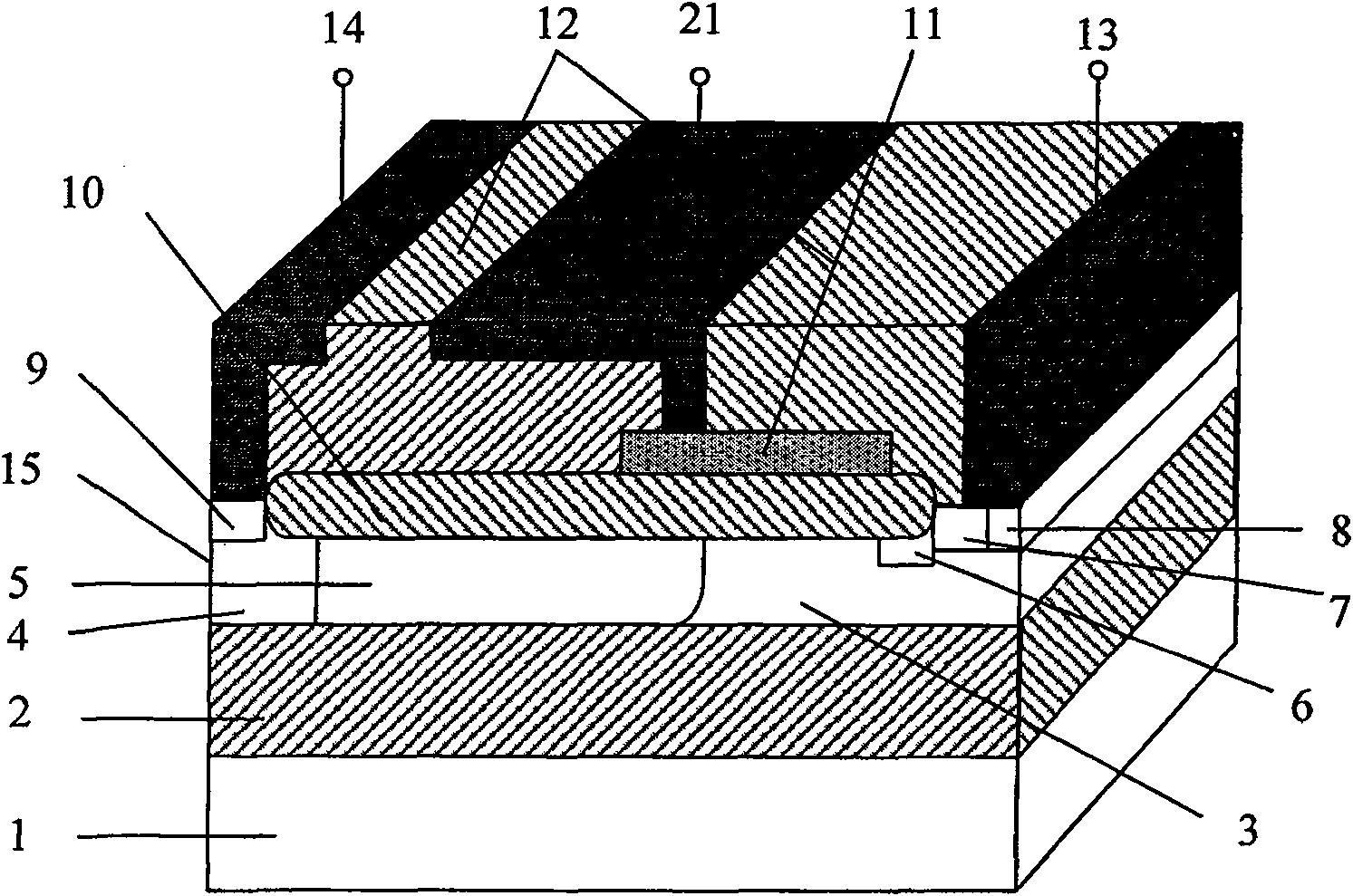

[0029] Thin film SOI new thick gate oxide power devices with gate field plate such as image 3 As shown, it includes substrate 1, buried oxide layer 2, SOI layer 15, body region 3, drift region 5, source extension region 6 under gate oxide, source region 7, well contact region 8, drain region well 4, drain region 9 , Thick gate oxide 10, interlayer dielectric 12, gate 11, source 13 and drain 14. It is characterized in that the SOI layer 15 is relatively thin, with a thickness of 1 μm to 2 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com