Making method for grid structure

A manufacturing method and gate structure technology, applied in the direction of semiconductor devices, etc., can solve the problems of increasing gates, device performance degradation, device failure, etc., to suppress the generation of gate root defects, uniform etching rate, and shorten the time interval Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 3 example

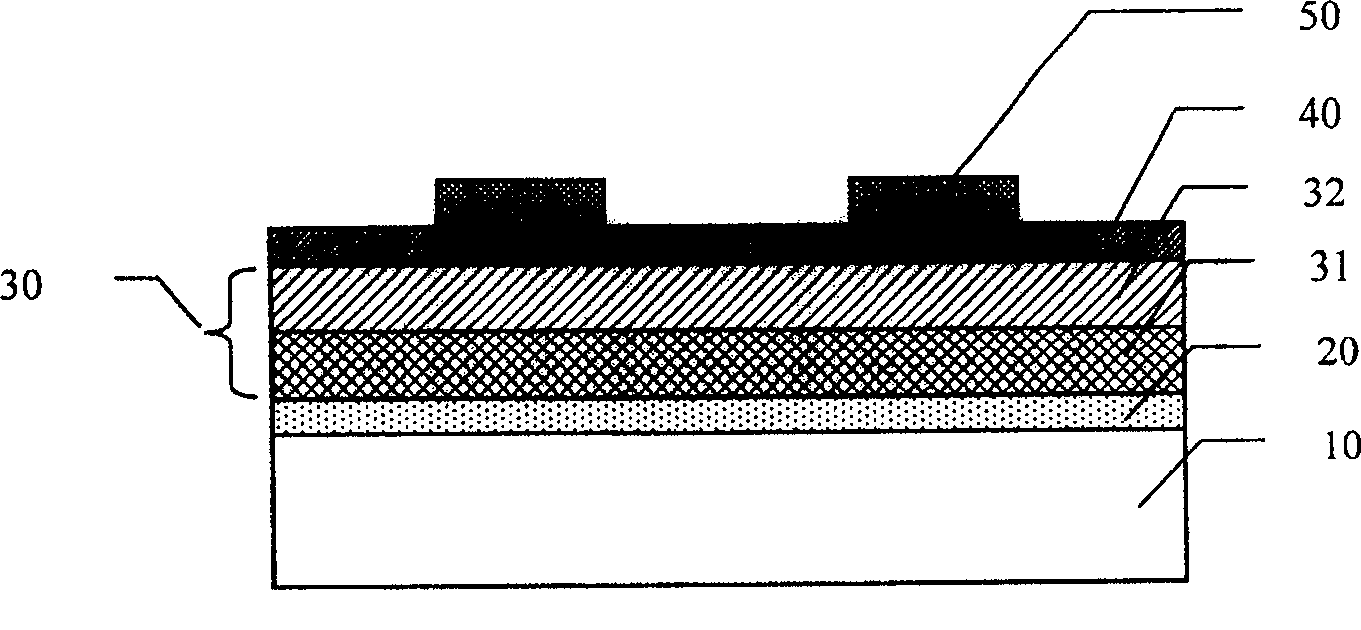

[0061] As the third embodiment of the method of the present invention, its specific implementation steps include:

[0062] Firstly, a dielectric layer, a conductive layer, a barrier layer and a patterned photoresist layer are sequentially deposited on the substrate. Wherein, the conductive layer includes a polysilicon layer and a metal layer deposited sequentially.

[0063] Then, using the patterned photoresist layer as a mask, the blocking layer is etched to obtain a blocking layer with an opening area; the opening area of the blocking layer exposes the upper surface of the metal layer.

[0064] Afterwards, the patterned photoresist layer is removed to obtain a smooth upper surface of the barrier layer and the metal layer.

[0065] Subsequently, the metal oxide is etched using the barrier layer with the opening region as a mask.

[0066] As an embodiment of the method of the present invention, the time interval between the removal of the patterned photoresist layer and th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com