Low-density odd-even checking codec hardware simulation system based on programmable gate array

A low-density parity, hardware emulation technology, applied in error detection coding using multi-bit parity bits, error correction/detection using block codes, special data processing applications, etc. problems such as rapid development problems, to achieve the effect of good noise quality, shortened simulation verification time, and good controllability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] The present invention will be described in further detail below in conjunction with the accompanying drawings. In the present embodiment, select the (2209,2021) Array LDPC code of code length N=2209 for use, the structure of this LDPC code is as attached Figure 5 shown. where I is the 47×47 identity matrix, α i is the matrix formed after the identity matrix I is shifted by i bits.

[0023] The input clock of the simulation system is 100MHz, and two clocks of 120MHz and 40Hz are obtained through processing by the digital phase-locked loop (DPLL) inside the FPGA. The entire FPGA hardware part operates at 40MHz except the decoder part, and the operating frequency of other parts is 120MHz.

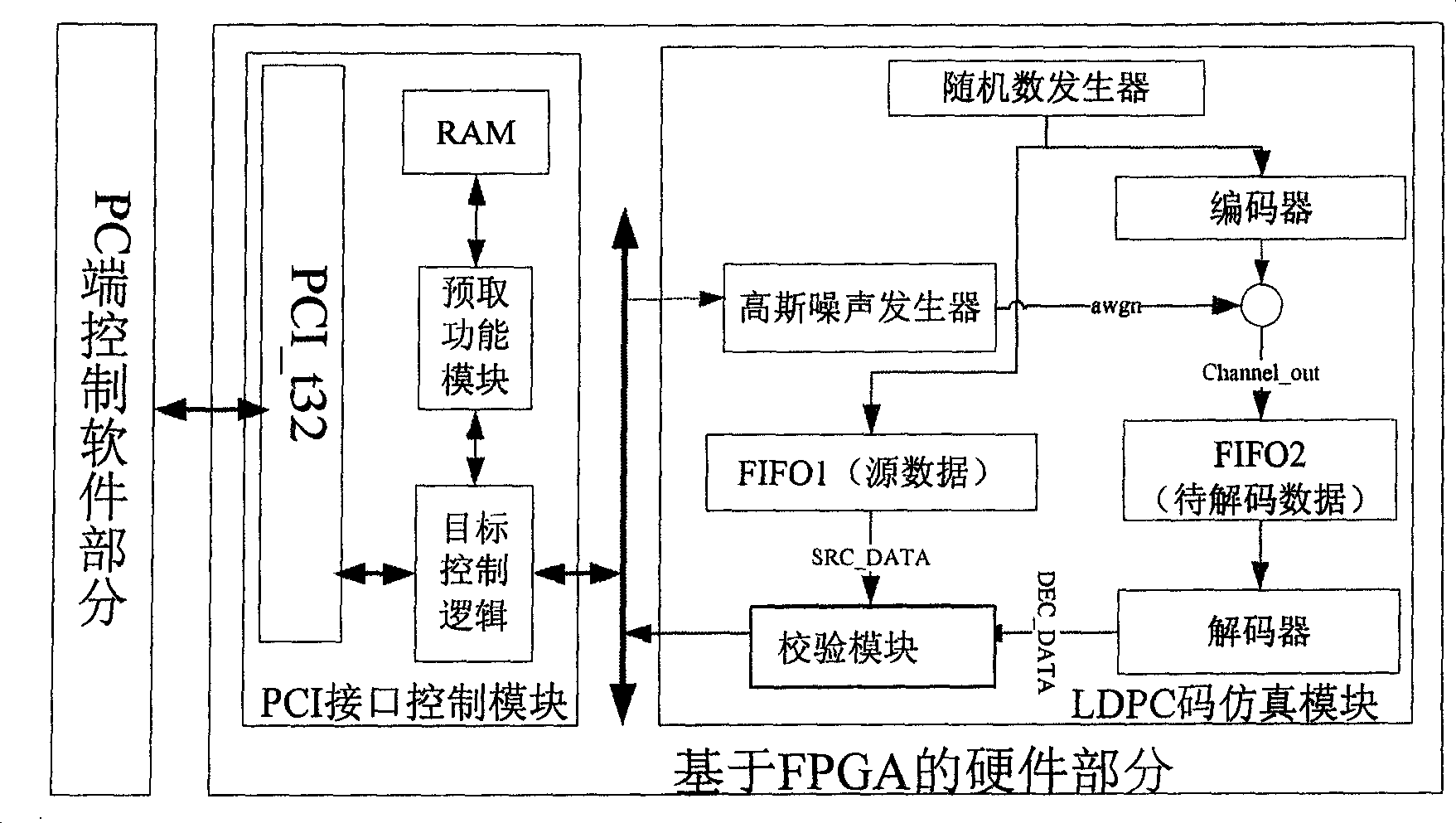

[0024] figure 1 It is a structural schematic diagram of the FPGA-based LDPC codec hardware emulation system of the present invention, and the system includes a PC-side control software part and an FPGA-based hardware part. FPGA hardware part includes PCI interface control module a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com