Random access memory initialization

A random access memory, random access storage technology, applied in static memory, digital memory information, information storage and other directions, can solve problems such as performance degradation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

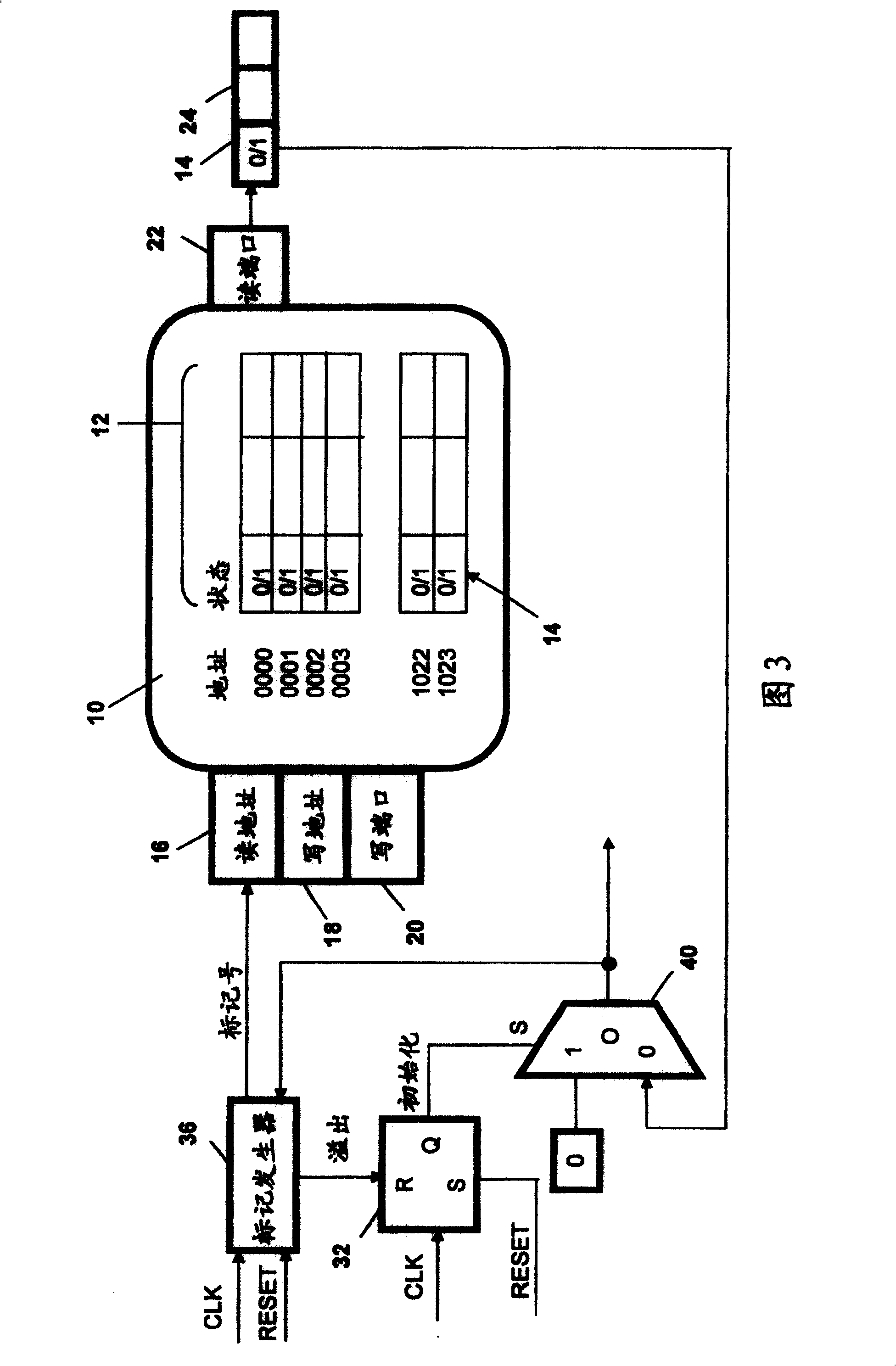

[0017] Figure 3 shows a memory structure embodying the invention, which should incorporate Figure 4 flow chart to read.

[0018] When a reset event occurs (step 50 ), a logic signal is clocked into the reset input of flag generator 36 and clocked into the S terminal of RS flip-flop 32 . Thus, the Q output of flip-flop 32 is set to logic "1" to indicate the initialization phase (step 52). A logic "1" is present at terminal S of the logic multiplexer 40, which results in a logic "0" output at the multiplexer output O (step 54). This is also fed back to the token generator 36 to indicate that all tokens are free to use and can be issued in sequence (step 56). As such, the tag state is assumed to be logic "0" to indicate that no tags are in use, even though some tags may be present in the memory address location.

[0019] In this example, tag generator 36 is free to issue tags via write address port 18 and update address space 12, starting at address 000 and proceeding to addre...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com