Method for removing lattice defect in pad area of semiconductor device

A lattice defect, semiconductor technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device testing/measurement, etc., can solve problems such as lattice defects in the pad area, not particularly reliable, and DRAM reliability impact

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment

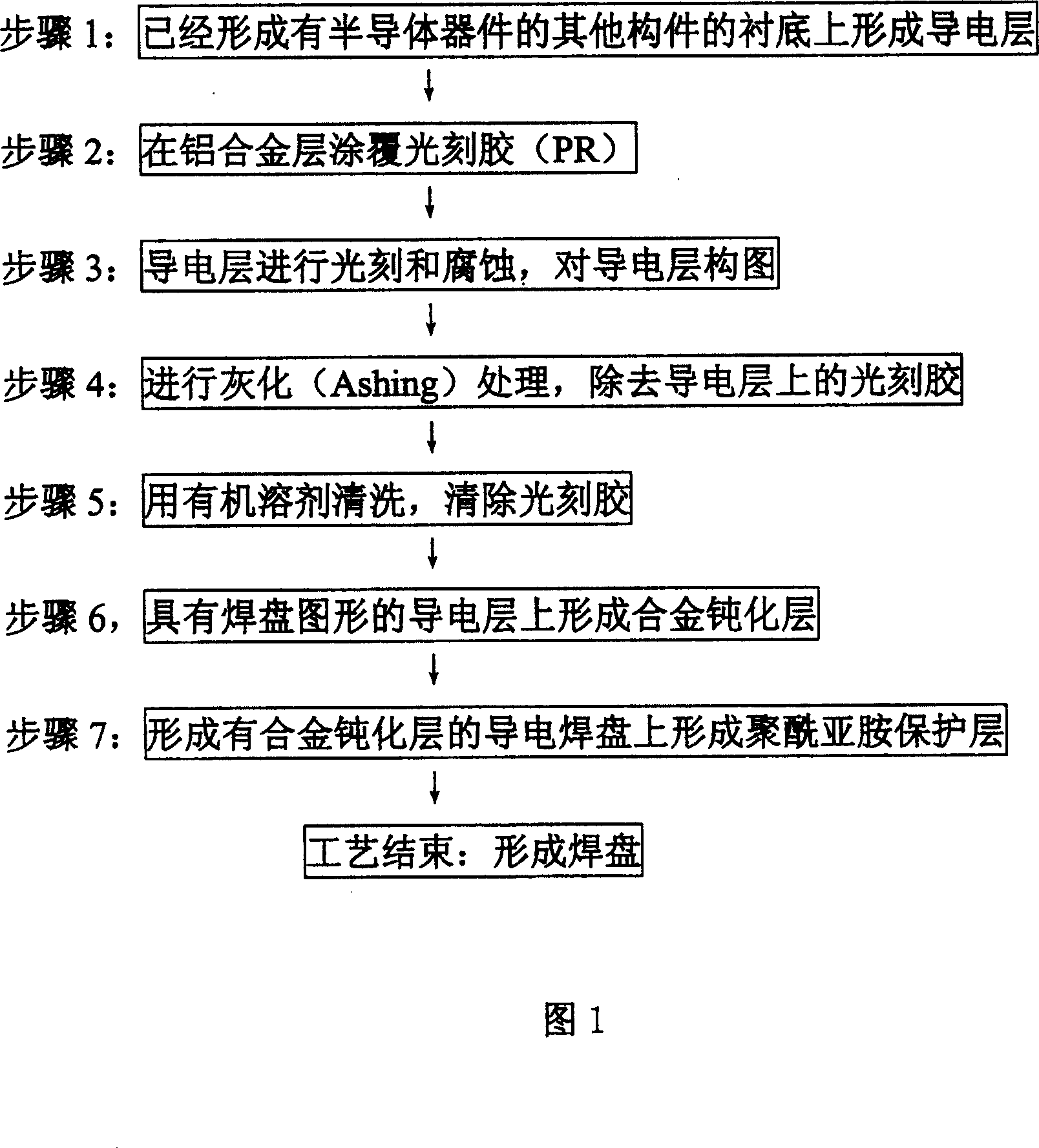

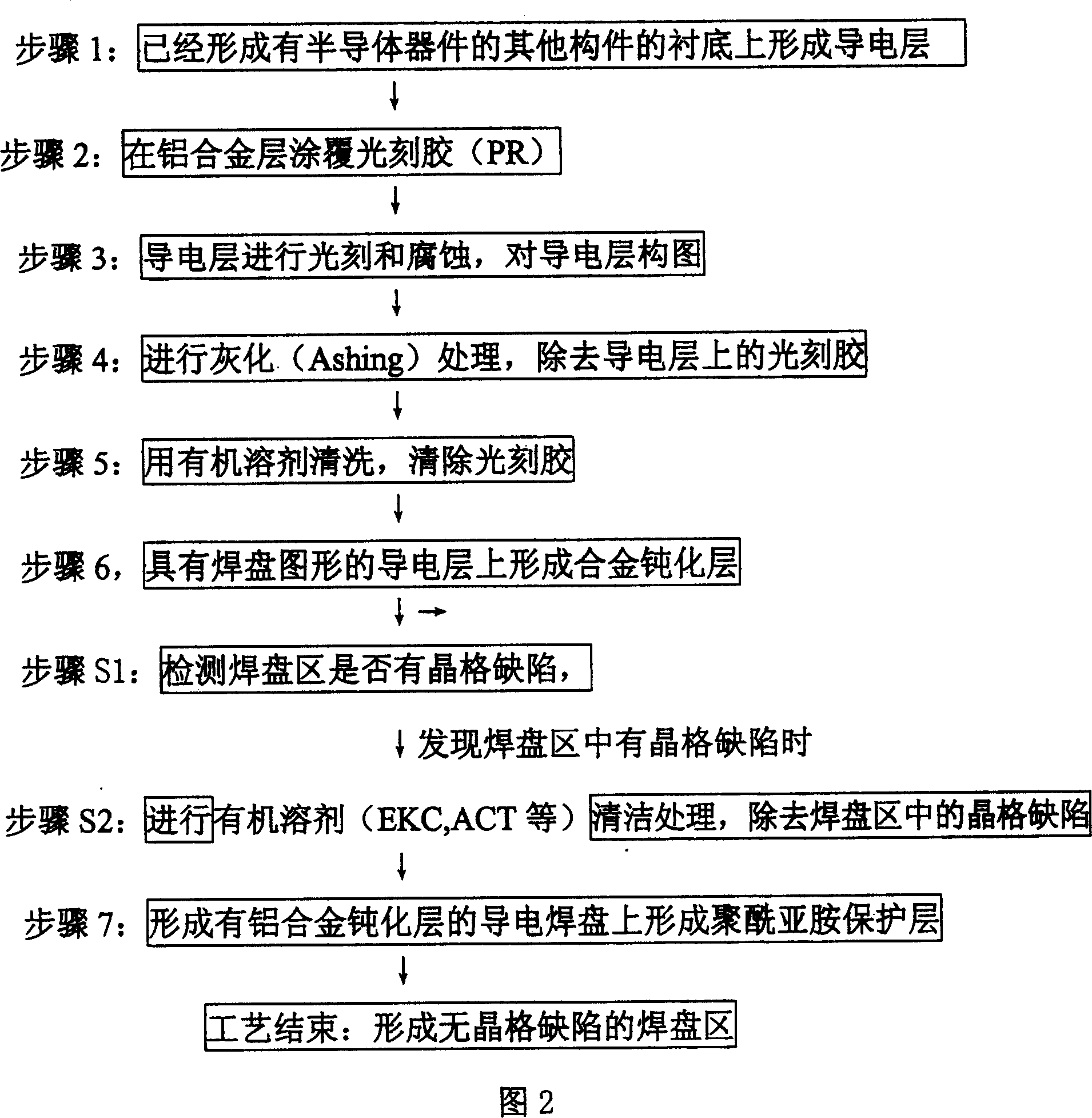

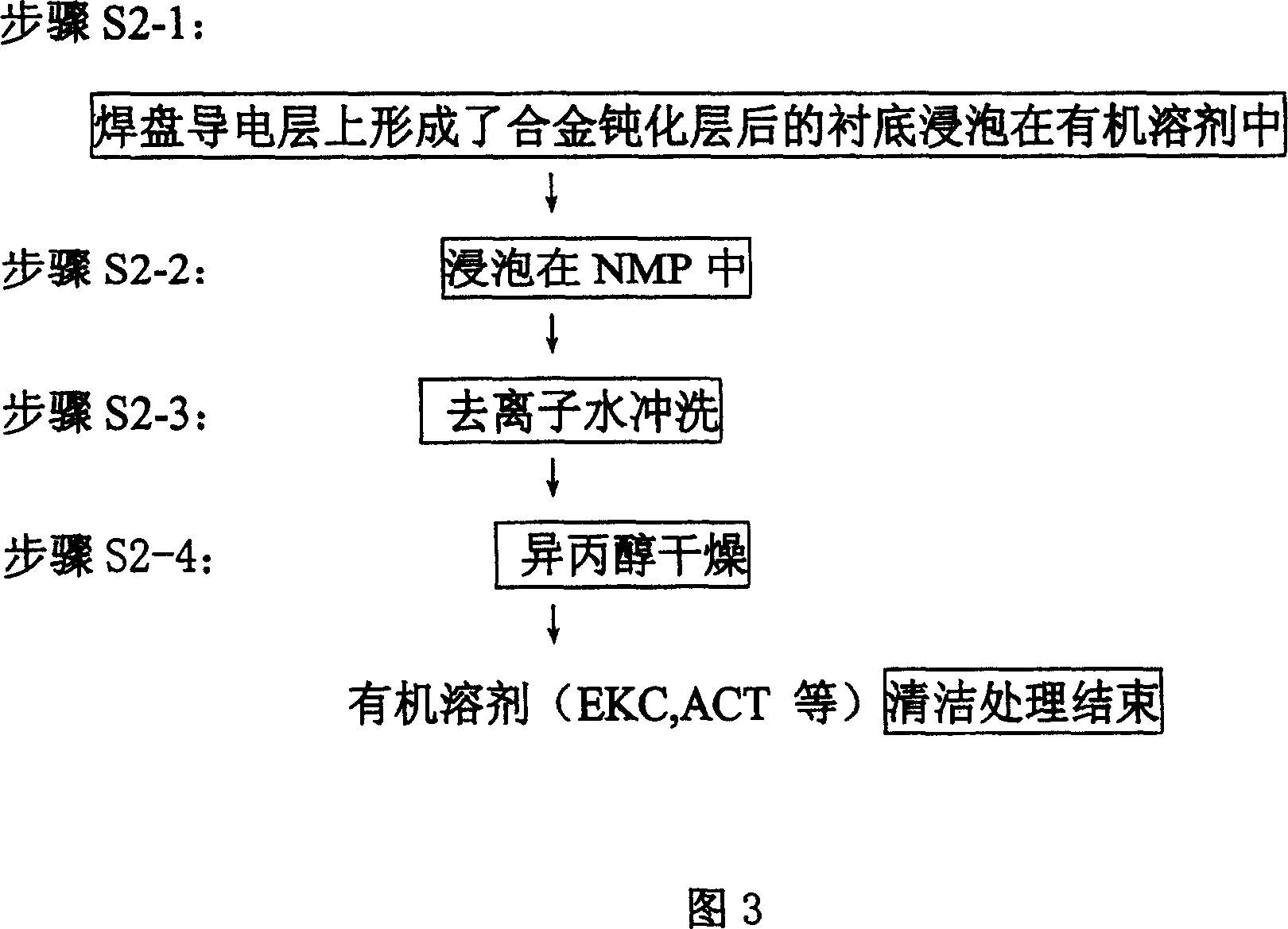

[0015] A method of cleaning and removing lattice defects in a pad (PAD) region of a semiconductor device with an organic solvent (EKC, ACT, etc.) according to the present invention will be described in detail below with reference to FIGS. 2 and 3 . Fig. 2 is a flowchart of a pad forming process of a semiconductor device according to the present invention. Fig. 3 is a flow chart of organic solvent (EKC, ACT, etc.) cleaning treatment.

[0016] The bonding pad forming process flow of the semiconductor device according to the present invention shown in Figure 2 is to increase step S1 (detection soldering) between step 6 and step 7 of the existing bonding pad forming process flow of the semiconductor device shown in Figure 1 Whether there is a lattice defect in the pad area); and step S2 (when step S1 detects that there is a lattice defect in the pad area, perform organic solvent (EKC, ACT, etc.) cleaning treatment). In step S1, use an optical microscope (OM) to detect whether the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com