Method of multi-level storage in DRAM and apparatus thereof

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

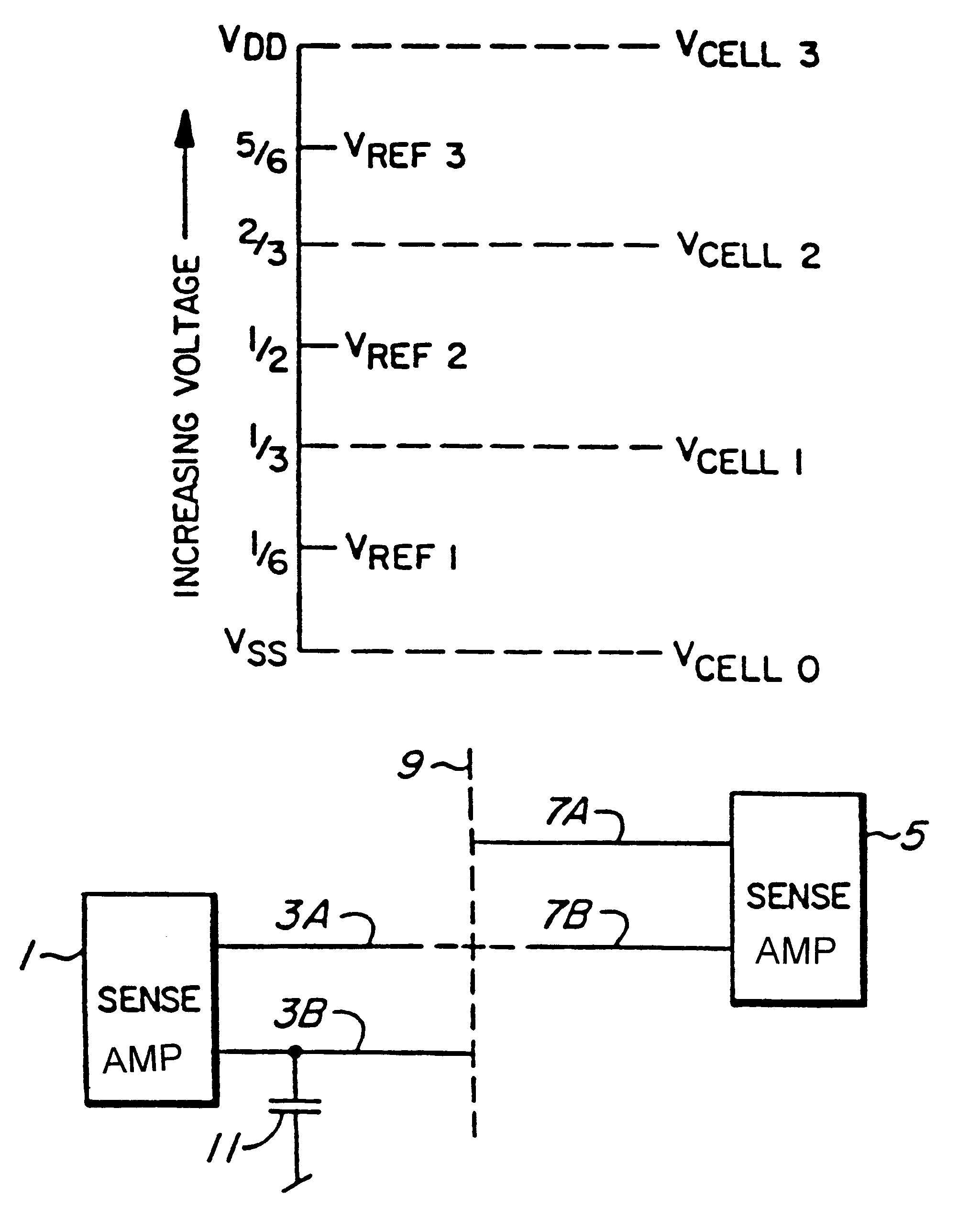

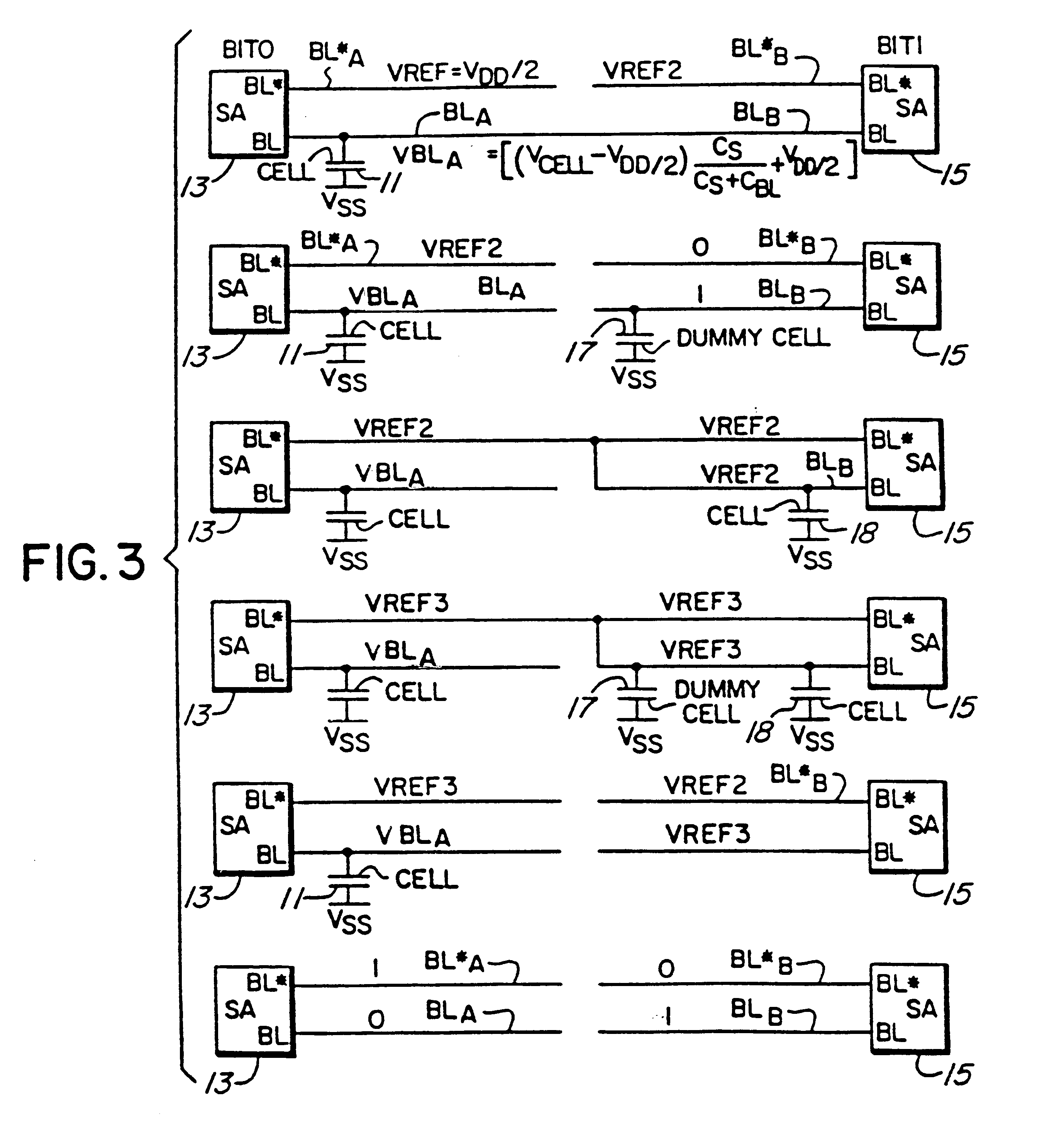

For a DRAM cell to store two bits using a single cell capacitor, the cell capacitor should store one of four voltage values V.sub.cell0, V.sub.cell1, V.sub.cell2 or V.sub.cell3, wherein V.sub.cell0 represents the lowest and V.sub.cell3 represents the highest cell voltage. To differentiate between the voltages, mid-point voltages V.sub.ref1 V.sub.ref2 and V.sub.ref3 are defined, as shown in FIG. 1. It may be seen that if the lowest actual cell voltage V.sub.cell0 is V.sub.SS or zero, V.sub.ref1 is one-sixth the highest voltage V.sub.DD, V.sub.cell1 is one-third V.sub.DD, V.sub.ref2 is one-half V.sub.DD, V.sub.cell2 is two-thirds V.sub.DD, V.sub.ref3 is five-sixths V.sub.DD and V.sub.cell3 equals V.sub.DD. Thus it may be sen that V.sub.ref1 is midway between V.sub.cell0 and V.sub.cell1, V.sub.ref2 is midway between V.sub.cell0 and V.sub.cell3 and V.sub.ref3 is midway between V.sub.cell2 and V.sub.cell3.

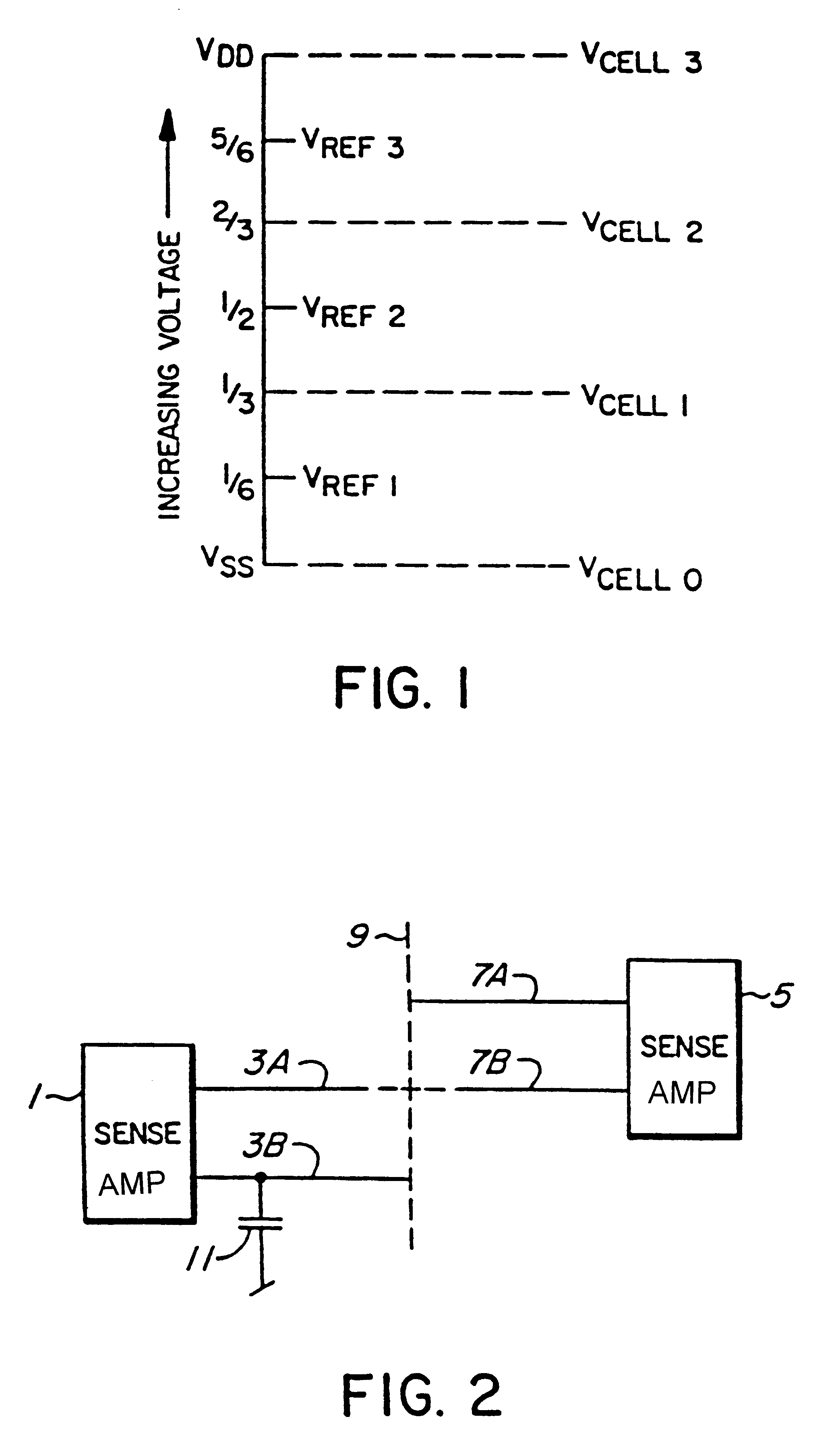

FIG. 2 will be used to illustrate the basic concept of the invention. A sense ampli...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com