Piggybacking of ECC corrections behind loads

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

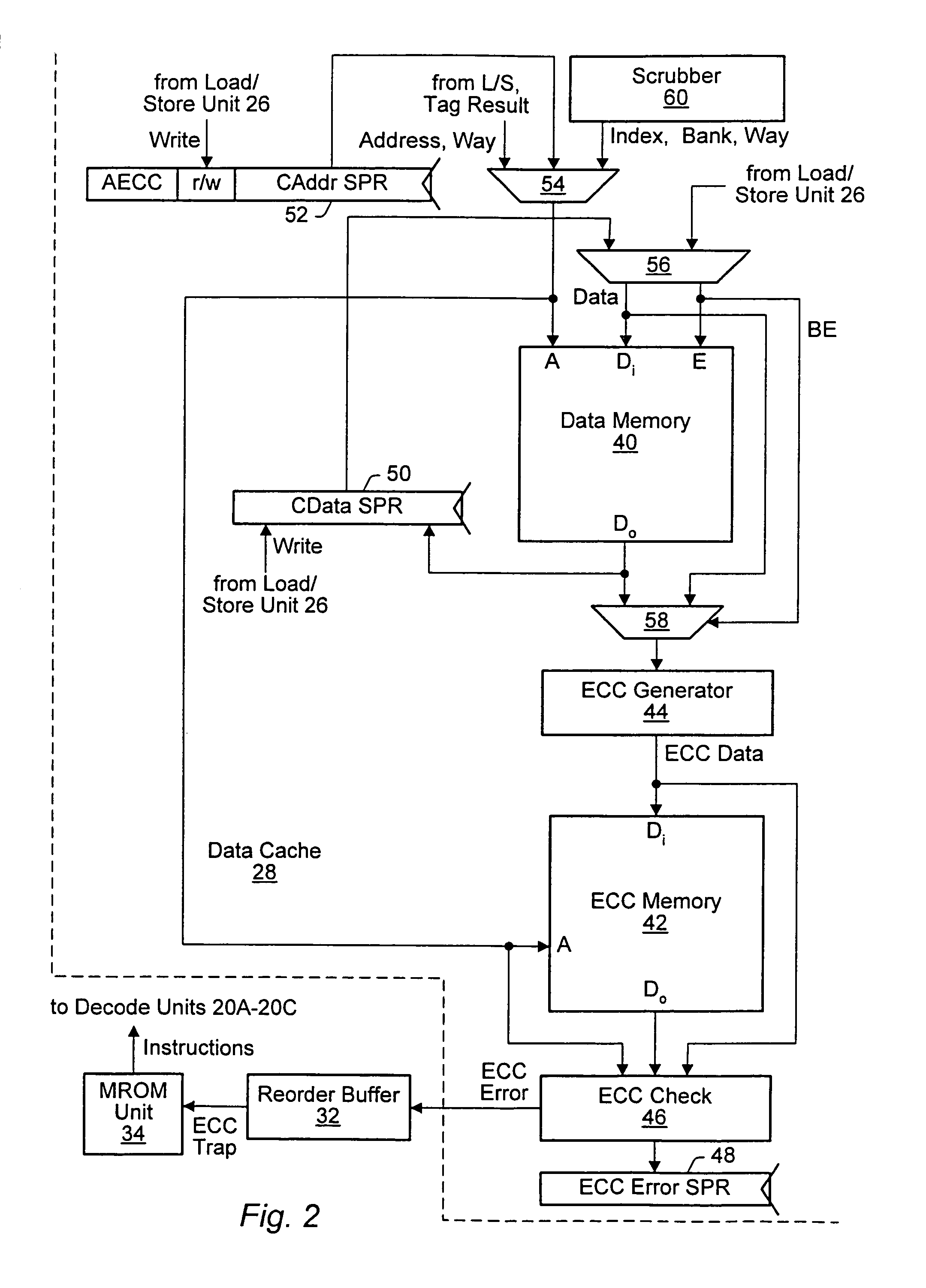

[0090]Turning next to FIG. 5, a flowchart illustrating a microcode routine for correcting ECC errors is shown. Other embodiments are possible and contemplated. The embodiment shown in FIG. 5 is an embodiment which uses the CAddr and CData SPRs 52 and 50 (and the autoECC generation, if applicable) to correct the ECC error. The blocks shown in FIG. 5 are illustrated in a particular order for ease of understanding. Other orders may be used. Generally, the blocks shown in FIG. 5 illustrate one or more instructions which, when executed (e.g. by functional units 24 and / or load / store unit 26) perform the functions illustrated in those blocks.

[0091]The microcode routine may determine whether the error is a correctable or uncorrectable ECC error (decision block 80). The type of error may be recorded in the reorder buffer 32, or may be recorded in an SPR such as the ECC error SPR 48. If the error is an uncorrectable ECC error, the microcode routine may trap to software (e.g. an operating syst...

second embodiment

[0097]Turning now to FIG. 6, a flowchart illustrating a microcode routine for correcting ECC errors is shown. Other embodiments are possible and contemplated. The embodiment shown in FIG. 6 is an embodiment which uses load / store instructions (executed by the load / store unit 26) to correct the ECC error (and thus the CAddr and CData SPRs may not be needed for this embodiment). The blocks shown in FIG. 6 are illustrated in a particular order for ease of understanding. Other orders may be used. Generally, the blocks shown in FIG. 6 illustrate one or more instructions which, when executed (e.g. by functional units 24 and / or load / store unit 26) perform the functions illustrated in those blocks.

[0098]Similar to the embodiment of FIG. 5, the microcode routine may optionally determine if the error is correctable or uncorrectable (and trap to software), and may read the ECC error SPR 48, check the valid bit, and exit without correcting the error if the valid bit is clear (blocks 80, 82, 84, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com