MMIC package

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

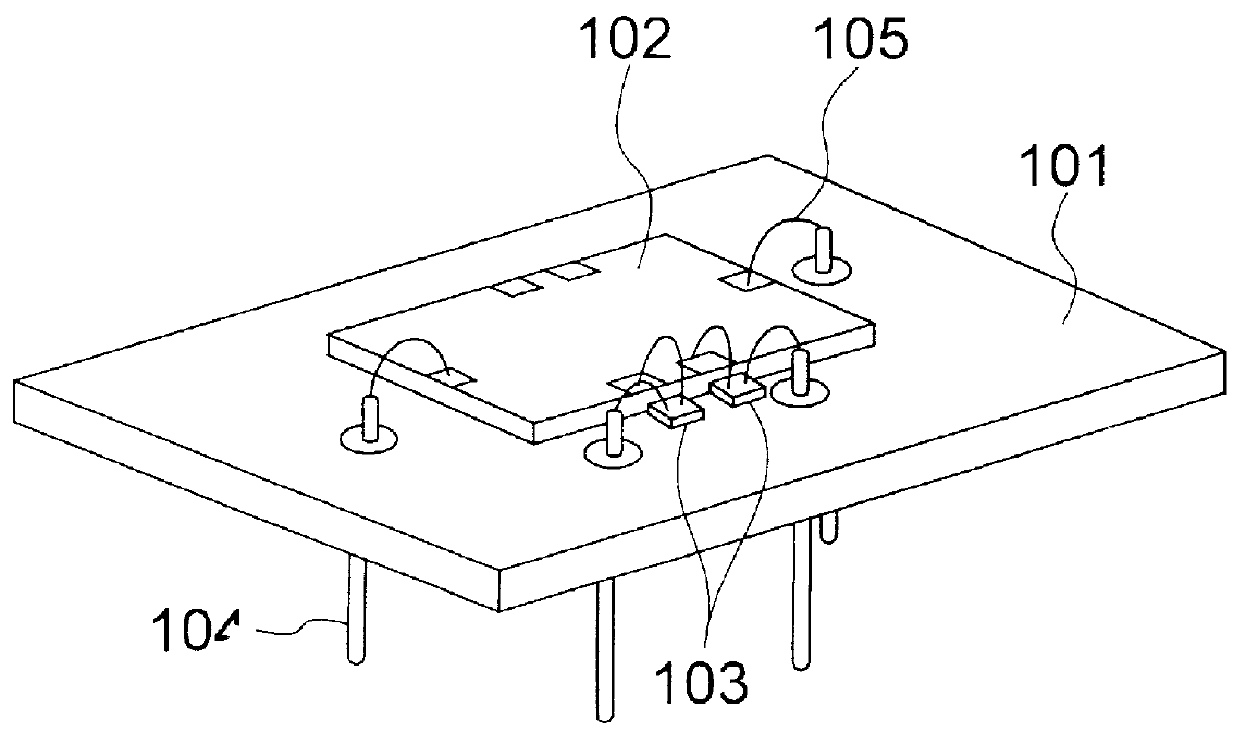

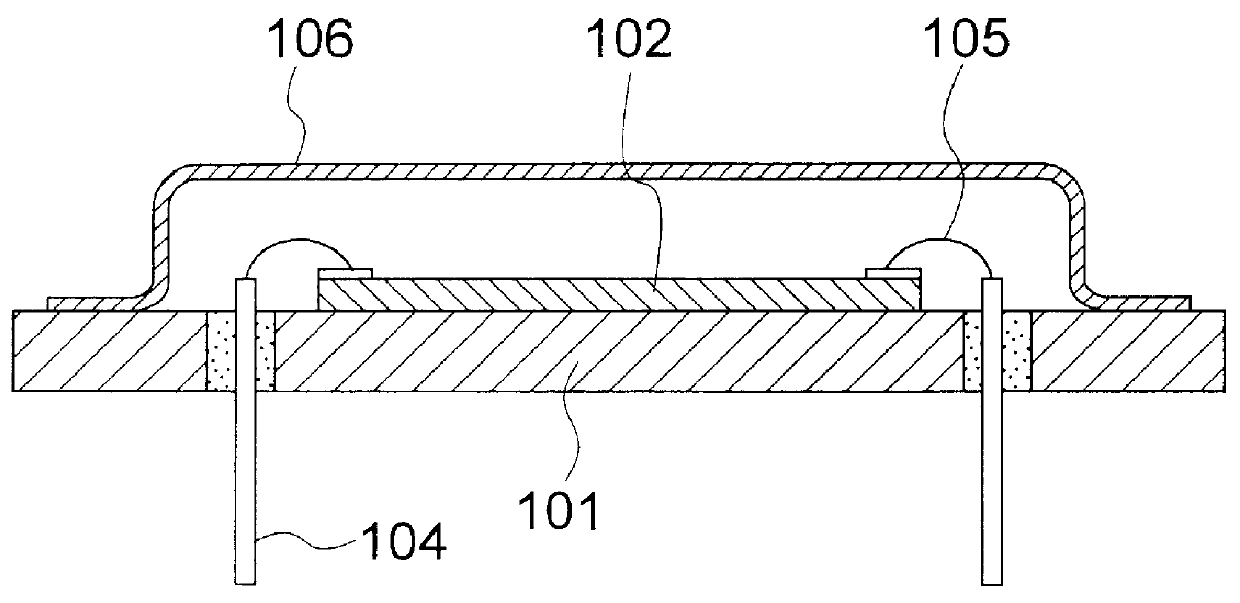

Image

Examples

embodiment 1

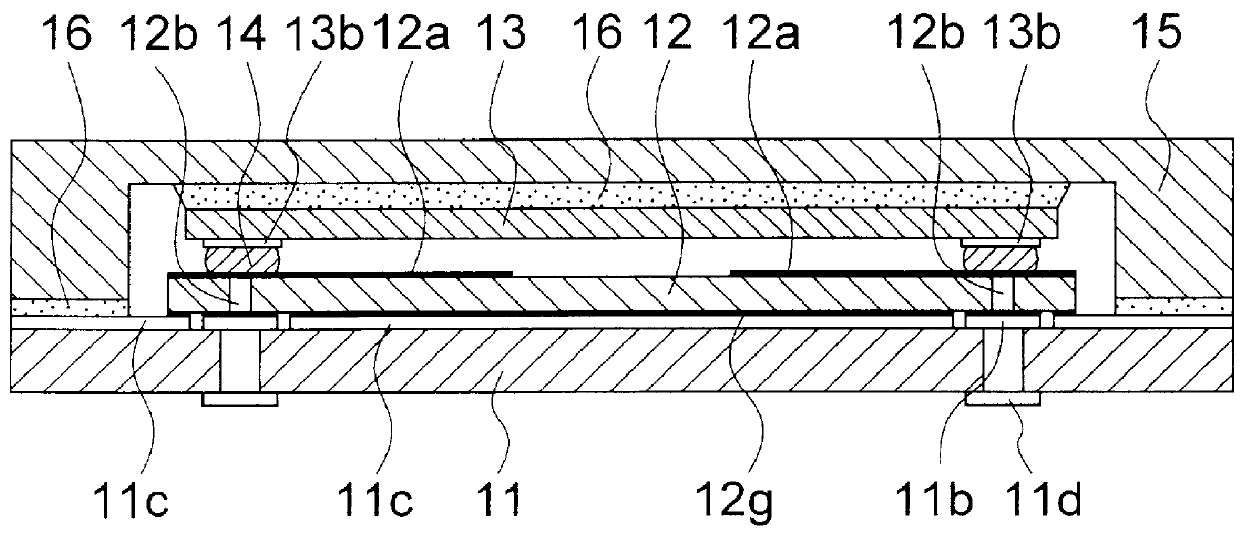

An MMIC package according to the first embodiment shown in FIG. 3 includes base substrate 11 made of ceramics material such as alumina. A signal terminal (not shown) and a source terminal 11b are formed on the top surface of the base substrate 11, and all the surface other than these elements is covered with a planar metal pattern 11c which functions as a GND terminal.

A plurality of pads 11d for connecting with another circuit substrate exist on the bottom surface of the base substrate 11. The respective pads 11d are connected with the above signal terminal (not shown), the source terminal 11b and the planar metal pattern 11c functioning as a GND terminal via through holes. As such, the MMIC package of the present Embodiment takes a so-called LCC (leadless chip carrier) structure.

On the base substrate 11 is mounted a composite capacitor substrate 12 and an MMIC is formed on this composite capacitor substrate 12 by means of the flip chip mounting, that is, by means of face-down bondi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com