Low-temperature selective epitaxial growth of silicon for device integration

a technology of epitaxial growth and silicon, applied in the field of low-temperature epitaxial growth process, can solve the problems of low silicon epitaxial growth rate, limited process and application, and high temperature requirement limit the use of silicon epitaxial growth,

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

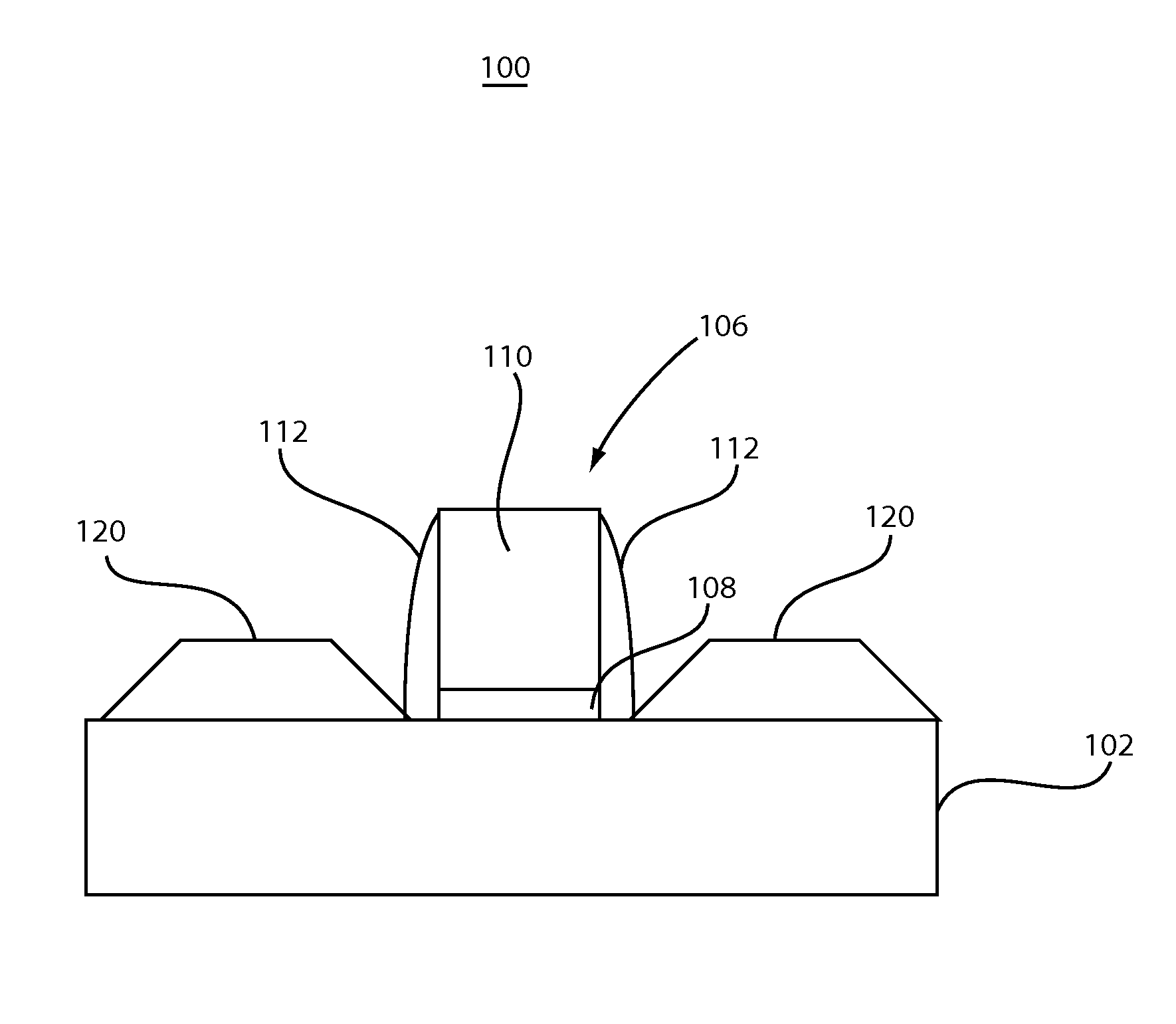

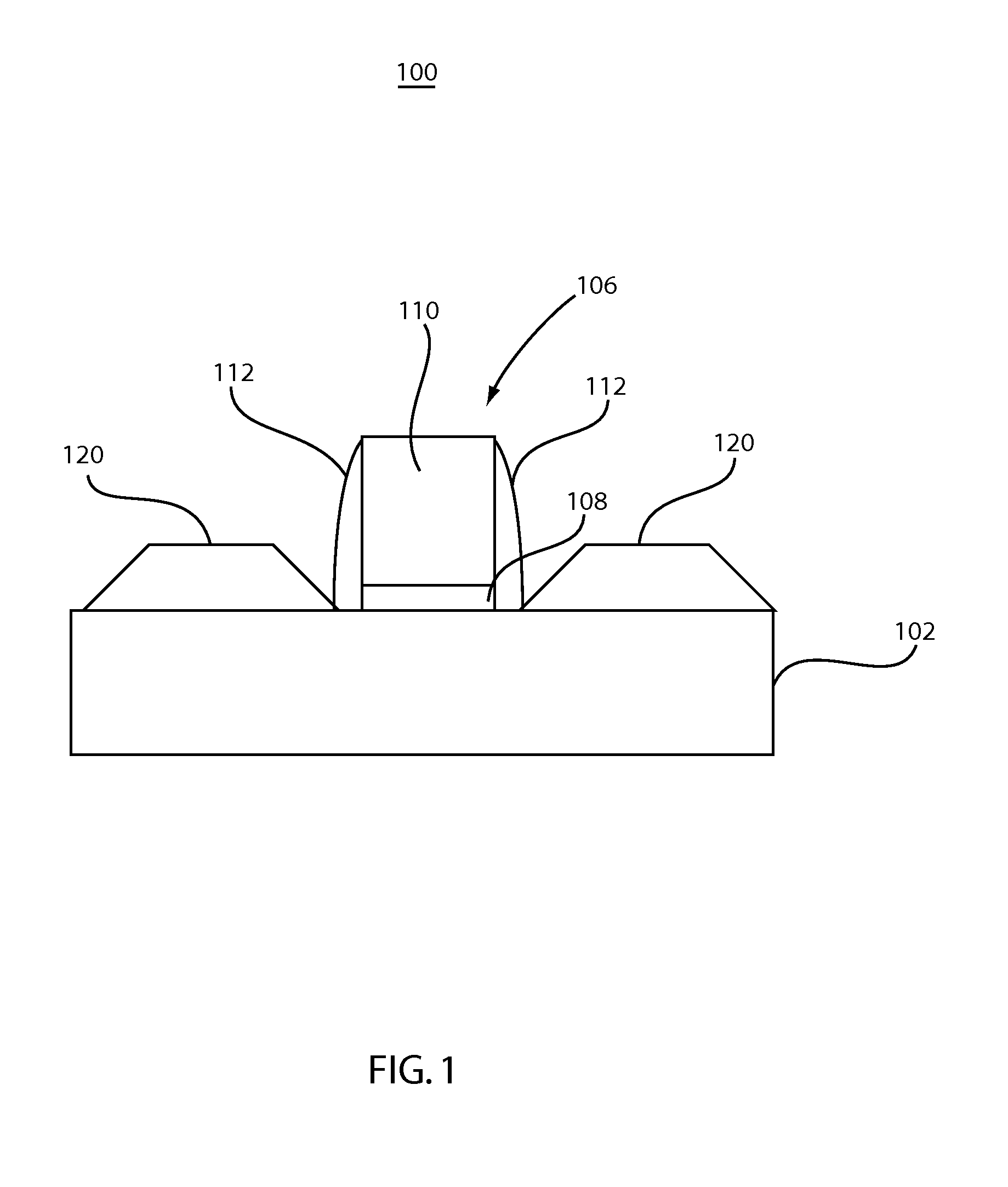

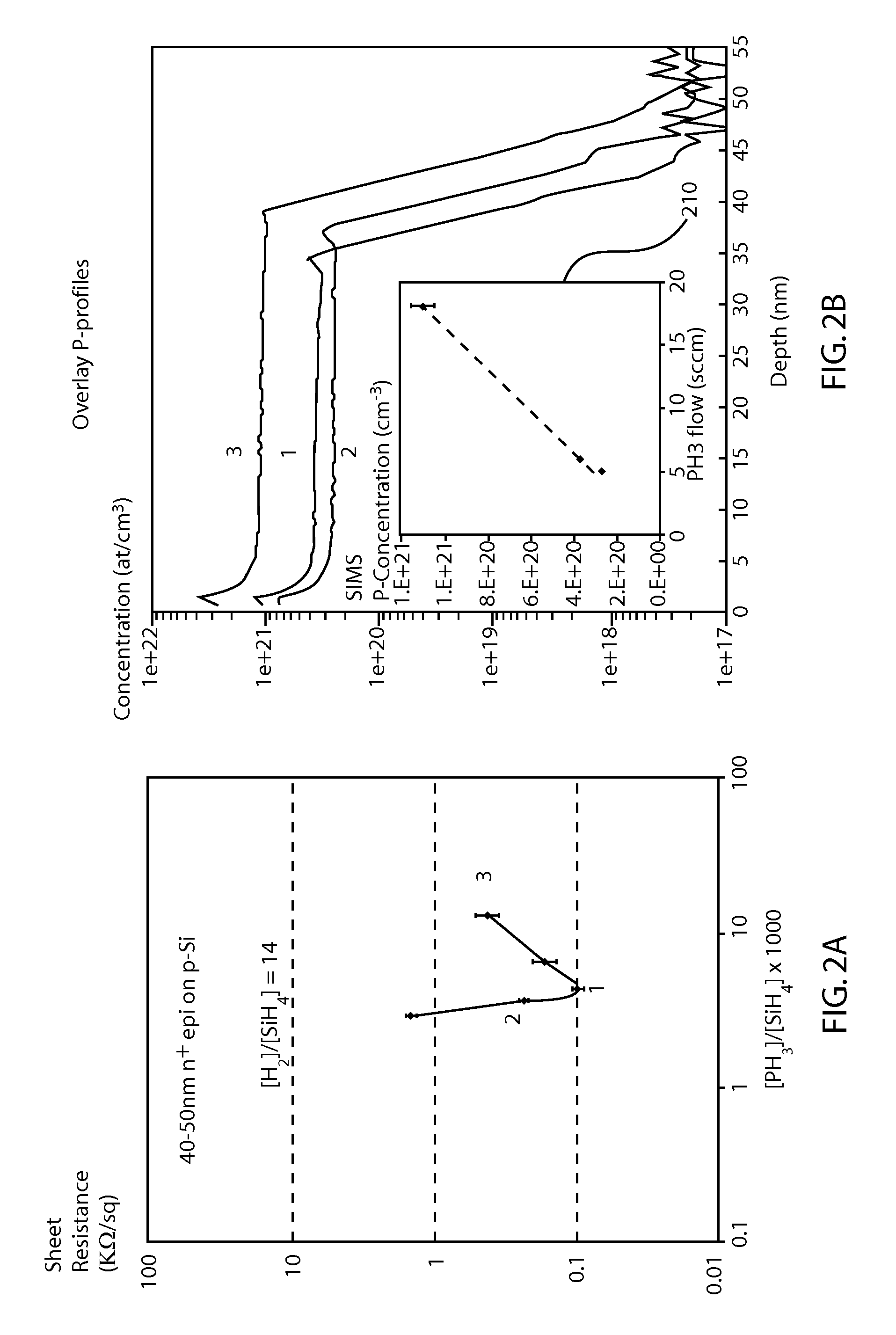

[0020]In accordance with the present principles, methods for selective epitaxial growth of highly-doped silicon at low temperatures are disclosed. In particularly useful embodiments, growth temperatures as low as 150° C. are achieved using plasma enhanced chemical vapor deposition (PECVD). The epitaxial growth is obtained by increasing and optimizing a gas ratio of [H2] / [SiH4]. In another embodiment, an N+ doped silicon is grown by, e.g., incorporating phosphorus using PH3 gas.

[0021]High dopant activation, e.g., greater than 1×1020 cm −3, can be obtained at 150° C. Selective growth is provided by etching a deposited silicon on regions where crystalline-Si (c-Si) is not exposed, in H2 plasma. As a result, the present embodiments offer an uninterrupted selective epitaxial growth (SEG) of Si, where the epitaxial growth and the plasma etching of the non-epitaxial Si occur in a same reactor. Selective epitaxial growth of boron doped Si or other dopants is also possible using the present ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| temperature | aaaaa | aaaaa |

| deposition temperature | aaaaa | aaaaa |

| temperatures | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com