Sidewall image transfer process employing a cap material layer for a metal nitride layer

a metal nitride layer and image transfer technology, applied in the direction of semiconductor/solid-state device manufacturing, basic electric elements, electric apparatus, etc., can solve the problems of loss or distortion of transfer pattern fidelity, and achieve high-fidelity reproduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

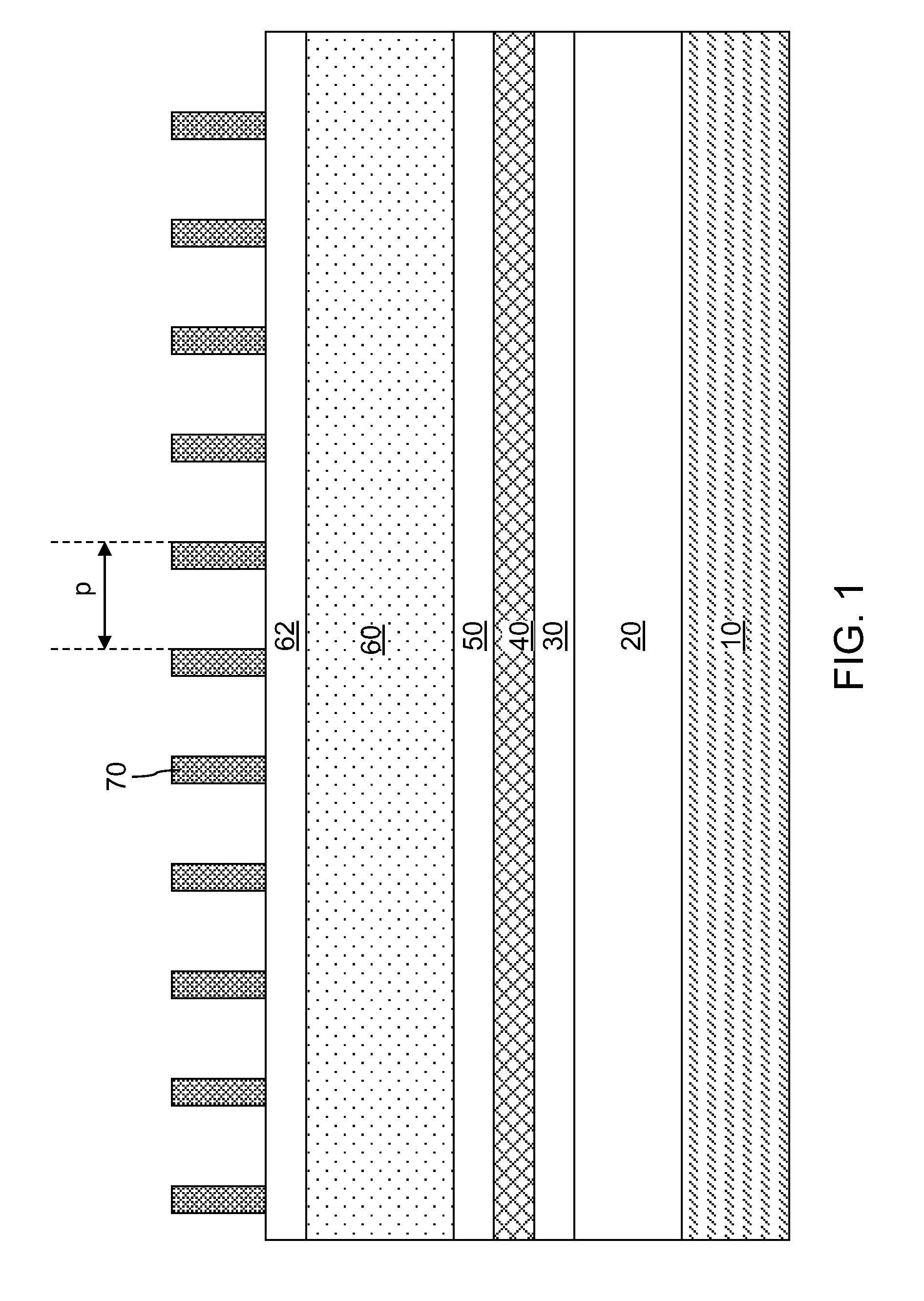

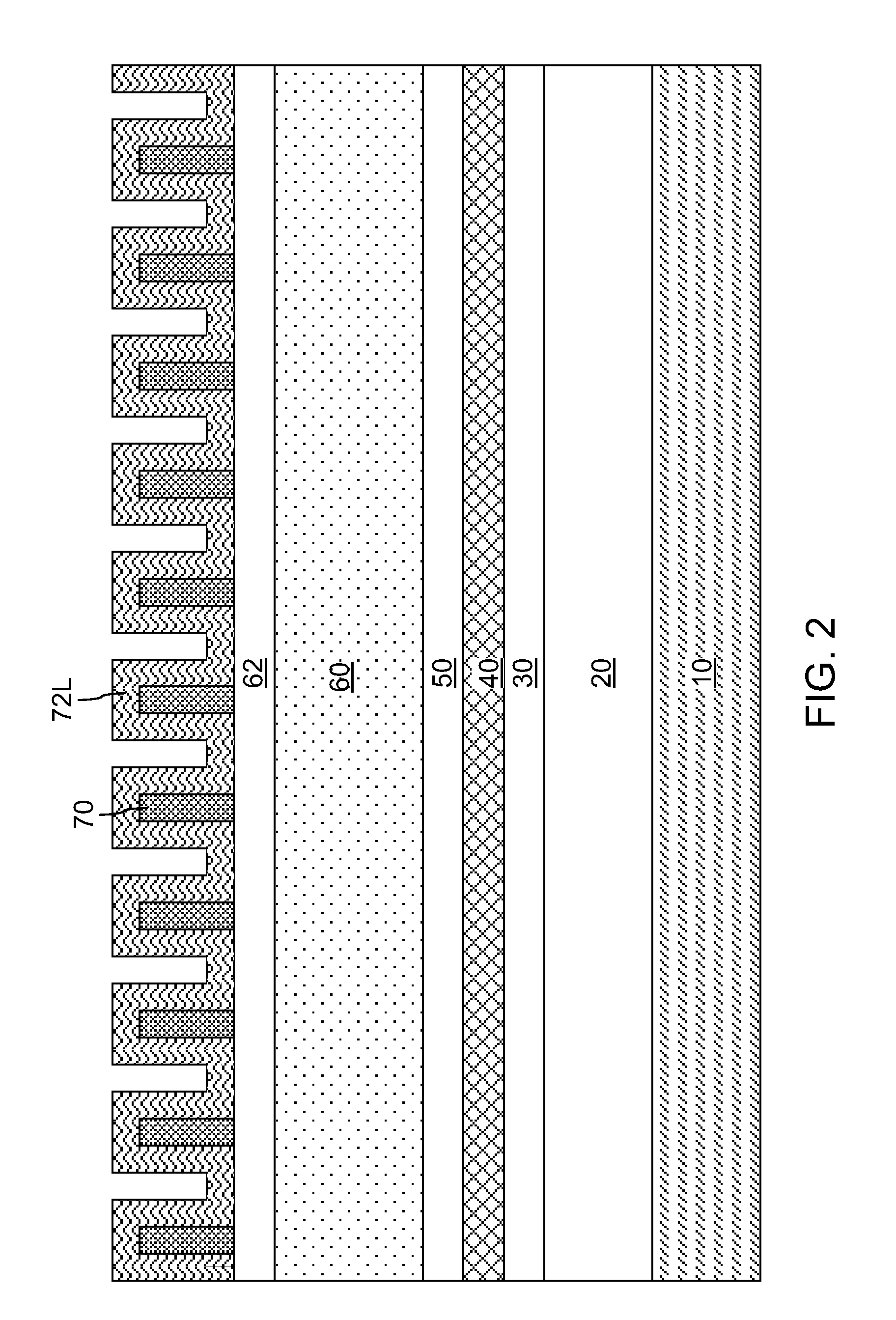

[0023]Referring to FIG. 1, a first exemplary structure according to the present disclosure includes a substrate 10 and a material stack formed thereupon. The substrate 10 can include a semiconductor substrate having semiconductor devices (not shown) therein. The semiconductor devices can include, for example, field effect transistors, junction transistors, diodes, resistors, capacitors, inductors, or any other semiconductor device known in the art. The substrate 10 may, or may not, include contact-level dielectric material layers (not shown) and / or interconnect level dielectric material layers (not shown) as well as embedded contact via structures (not shown) and / or embedded wiring level metal interconnect structures. Alternately, the topmost portion of the substrate 10 can include a semiconductor material such as single crystalline silicon.

[0024]An underlying material layer 20 can be formed on the substrate 10. The underlying material layer 20 can be a single dielectric material la...

second embodiment

[0060]Referring to FIG. 12, a second exemplary structure according to the present disclosure can be derived from the first exemplary structure by extending the duration of the etch and the depth of the trenches 21 at a processing step corresponding to FIG. 10. The trenches 21 are extended to the bottom of the underlying material layer 20 at the end of the etch step.

[0061]Referring to FIG. 13, conductive line structures 22 are formed within the underlying material layer 20 employing the same processing steps as in the first embodiment.

third embodiment

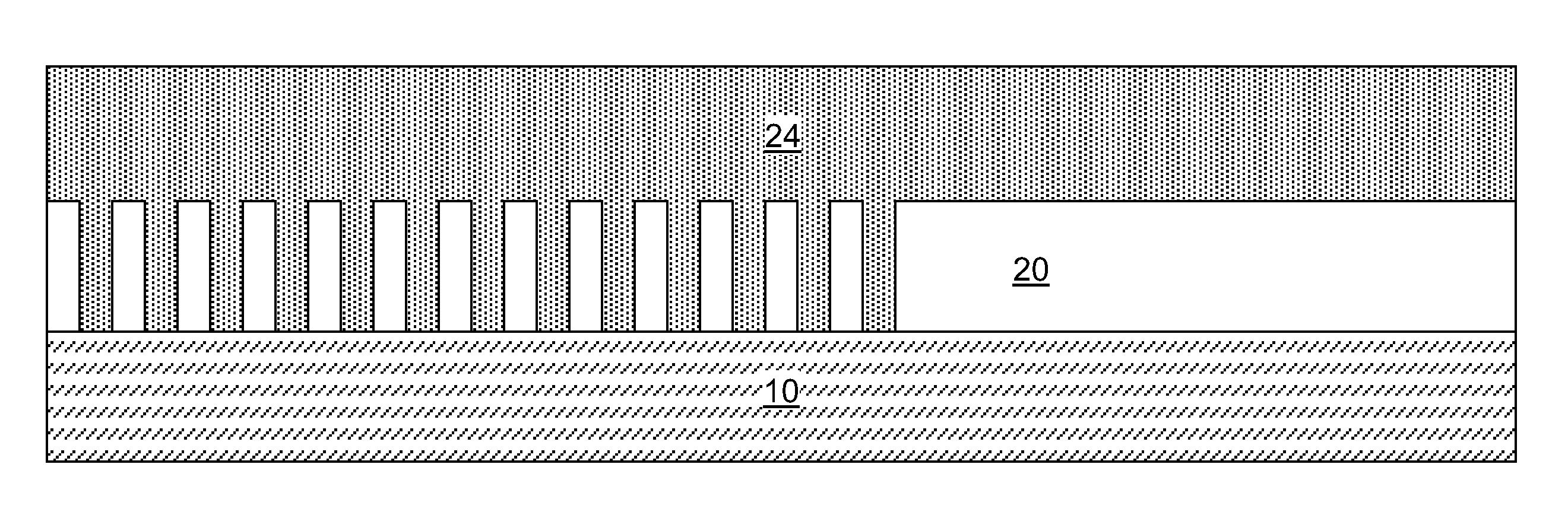

[0062]Referring to FIG. 14, in a third exemplary structure according to the present disclosure, the underlying material layer 20 can include a conductive material. The trenches 21 are formed through the underlying material layer 20 to the top surface of the substrate 10, which may include a dielectric surface. The underlying material layer 20 can be patterned into multiple conductive portions that do not contact one another.

[0063]Referring to FIG. 15, a dielectric material layer 24 can be deposited over the patterned underlying material layer 20 to provide electrical isolation between the various conductive portions of the patterned underlying material layer 20. Optionally, additional conductive structures (not shown) may be formed in an upper portion of the dielectric material layer 24 to provide electrical connections among the various conductive portions of the underlying material layer 20.

PUM

| Property | Measurement | Unit |

|---|---|---|

| thicknesses | aaaaa | aaaaa |

| thicknesses | aaaaa | aaaaa |

| thicknesses | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com