Method of fabricating polycrystalline silicon layer, TFT fabricated using the same, method of fabricating TFT, and organic light emitting diode display device having the same

a technology of polycrystalline silicon and thin film transistor, which is applied in the direction of transistors, solid-state devices, thermoelectric devices, etc., can solve the problems of long processing time and risk of substrate transformation, poor interfacial characteristics between a semiconductor layer and a gate insulating layer, and high cost of laser equipment. achieve the effect of reducing leakage curren

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

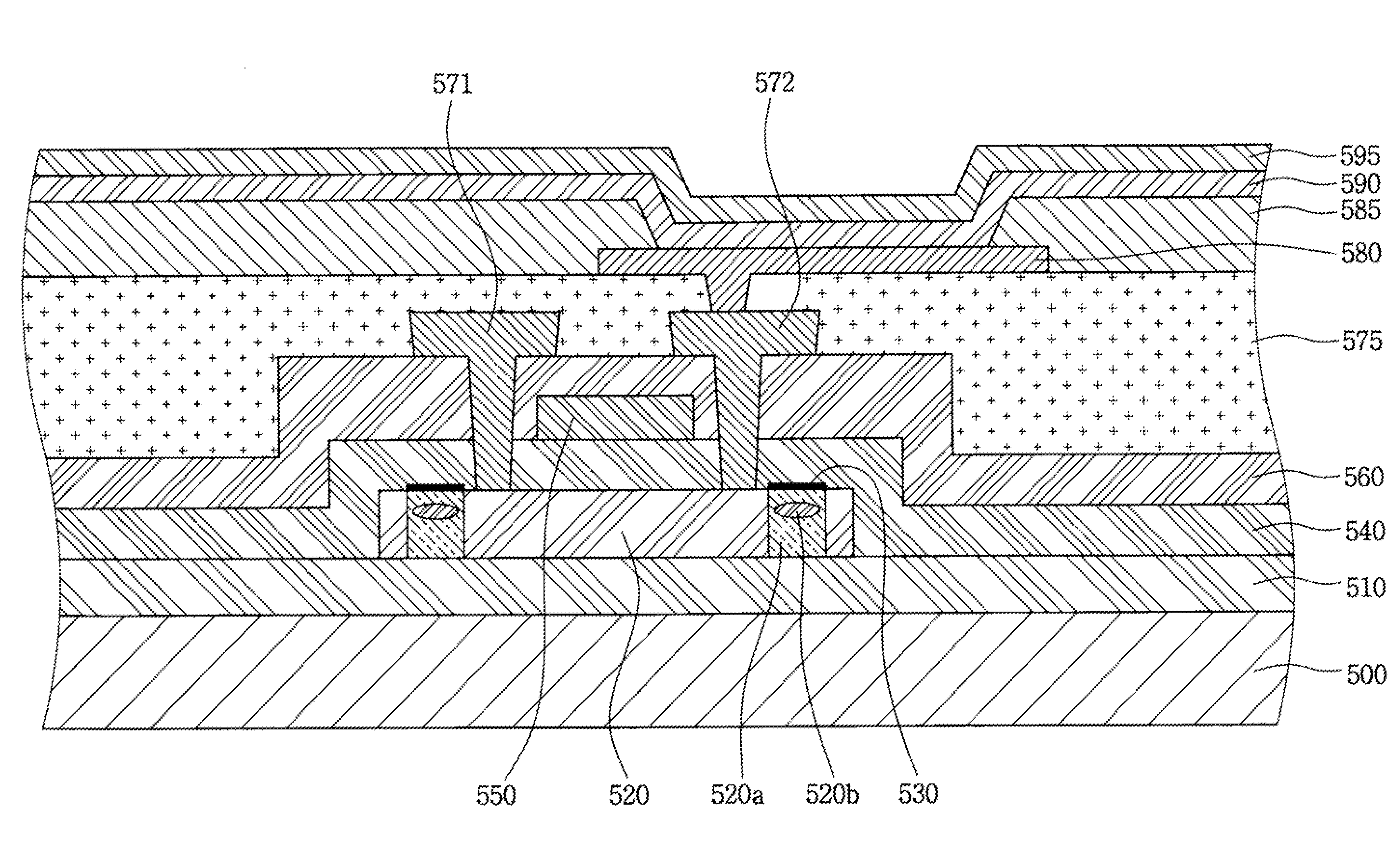

[0027]Reference will now be made in detail to the present embodiments of the present invention, examples of which are illustrated in the accompanying drawings, wherein like reference numerals refer to the like elements throughout. The embodiments are described below in order to explain the present invention by referring to the figures.

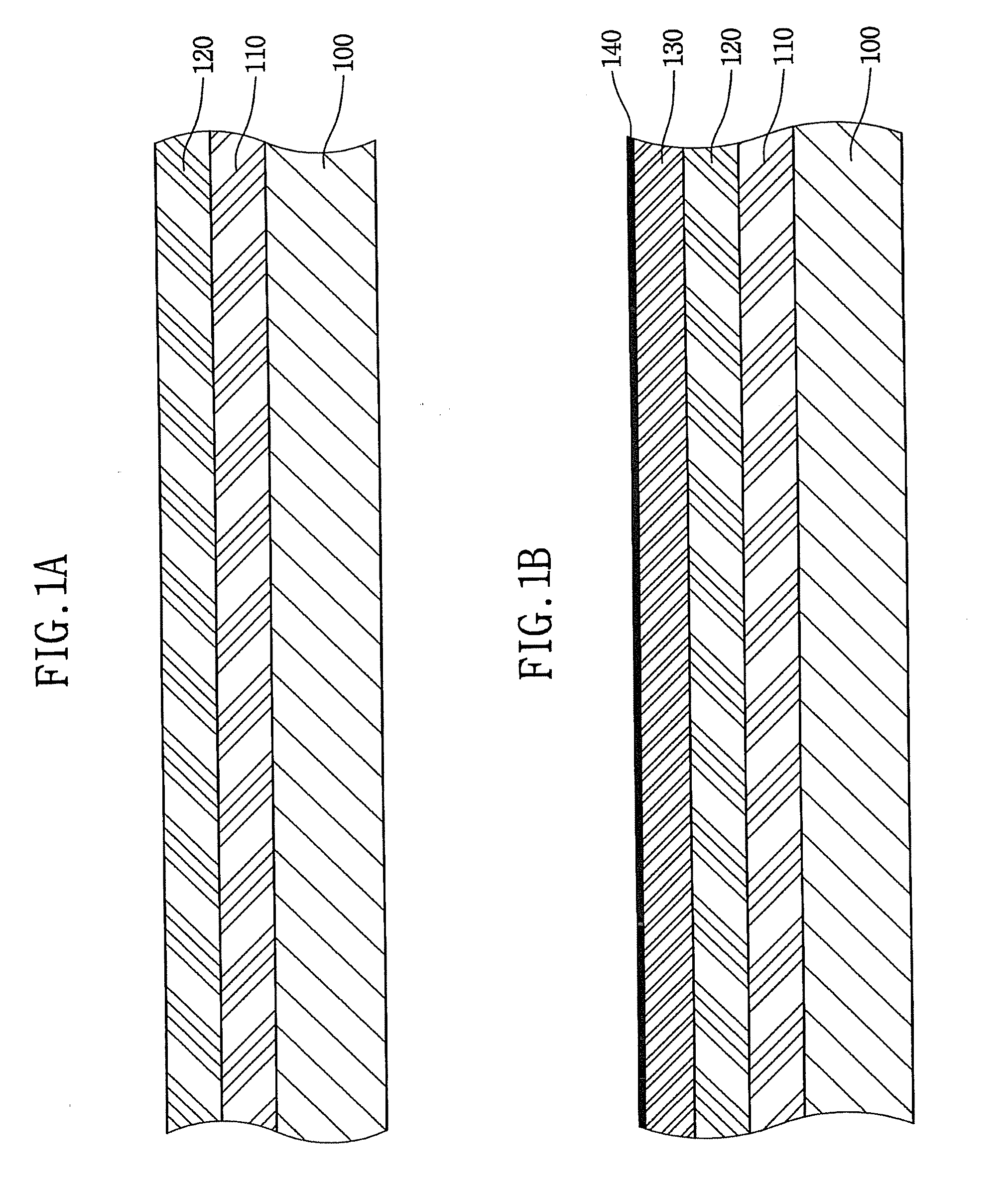

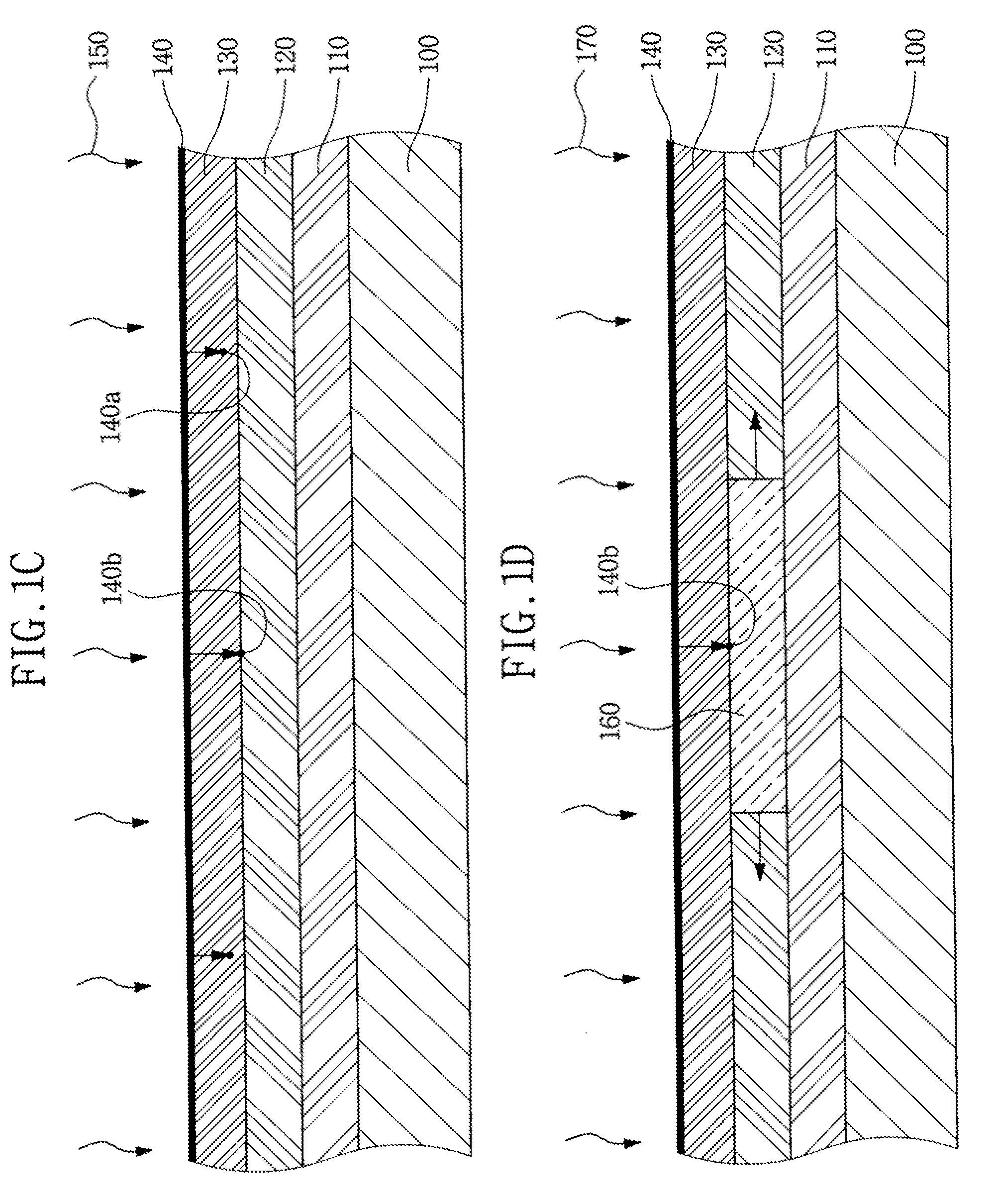

[0028]FIGS. 1A to 1D are cross-sectional views illustrating a crystallization process according to an embodiment of the present invention.

[0029]First, as illustrated in FIG. 1A, a buffer layer 110 may be formed on a substrate 100, which is formed of glass or plastic. The buffer layer 110 is an insulating layer and may be formed of silicon oxide, silicon nitride or a combination thereof by chemical vapor deposition (CVD) or physical vapor deposition (PVD). The buffer layer 110 serves to prevent the diffusion of moisture or impurities occurring in the substrate 100 or to adjust the heat transfer rate during crystallization, thereby allowing crystallizati...

PUM

| Property | Measurement | Unit |

|---|---|---|

| distance | aaaaa | aaaaa |

| diffusion coefficient | aaaaa | aaaaa |

| temperature | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com