SELF-ALIGNED PROCESS FOR NANOTUBE/NANOWIRE FETs

a nanotube and nanowire technology, applied in the field of semiconductor structure, can solve the problem of not having a self-aligning process comparable to conventional cmos technology

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

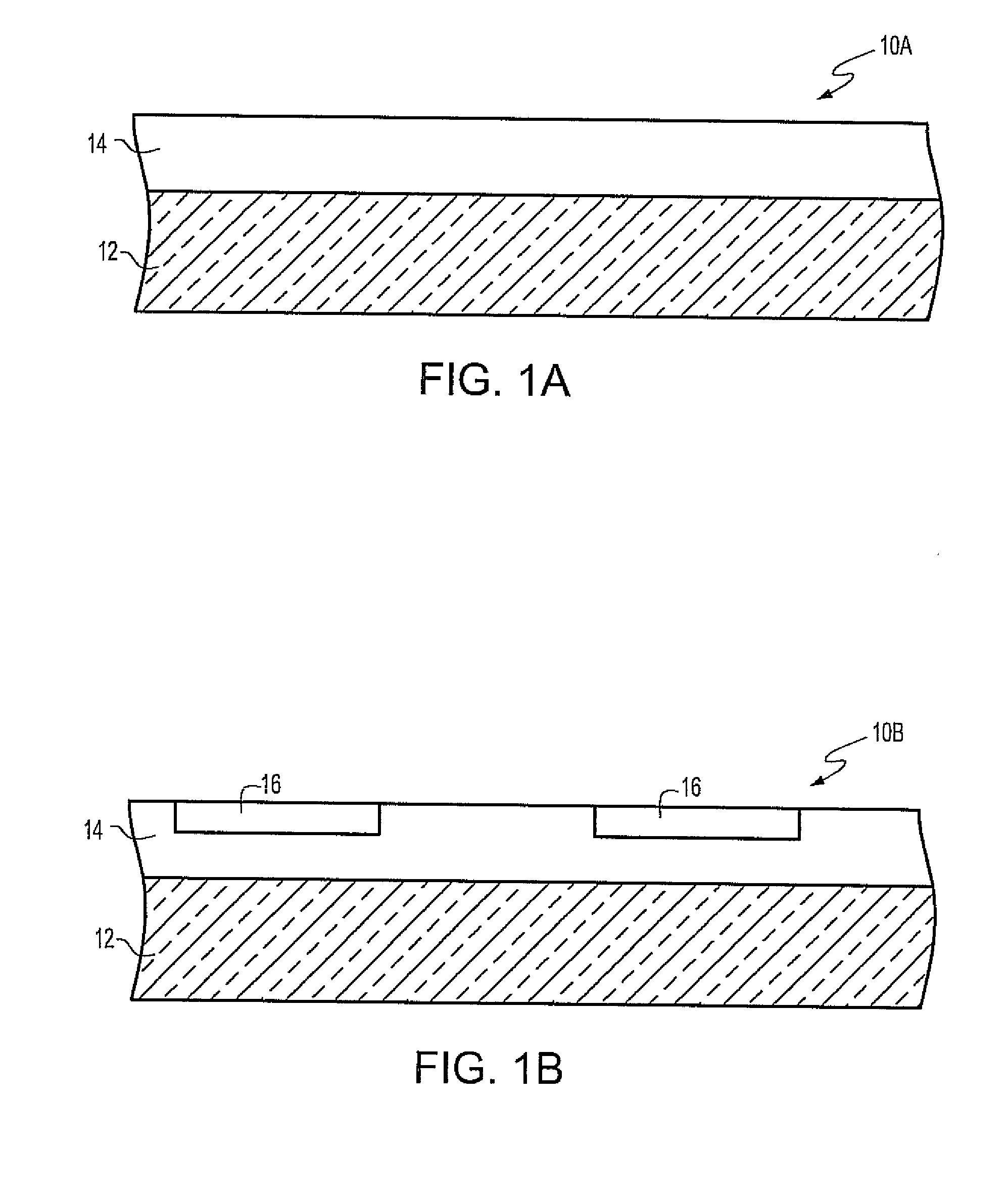

[0034] The present invention, which provides a one-dimensional nanostructure-containing FET and a method of fabricating the same, will now be described in greater detail by referring to the drawings that accompany the present application. The various drawings of the present invention are provided for illustrative purposes and thus they are not drawn to scale. Also, the drawings depict the presence of a single gate region; the term “gate region” is used herein to denote the gate, gate electrode and underlying device channel. Although a single gate region is depicted and described, the present invention also contemplates forming a plurality of such gate regions and thus a plurality of one-dimensional nanostructure-containing FETs on a surface of a substrate.

[0035] The present invention begins with first providing the initial substrate shown in either FIG. 1A or FIG. 1B. The initial substrate 10A shown in FIG. 1A comprises a semiconductor layer 12 which includes a dielectric layer 14 ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| temperature | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com