Semiconductor device having a plurality of semiconductor constructs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

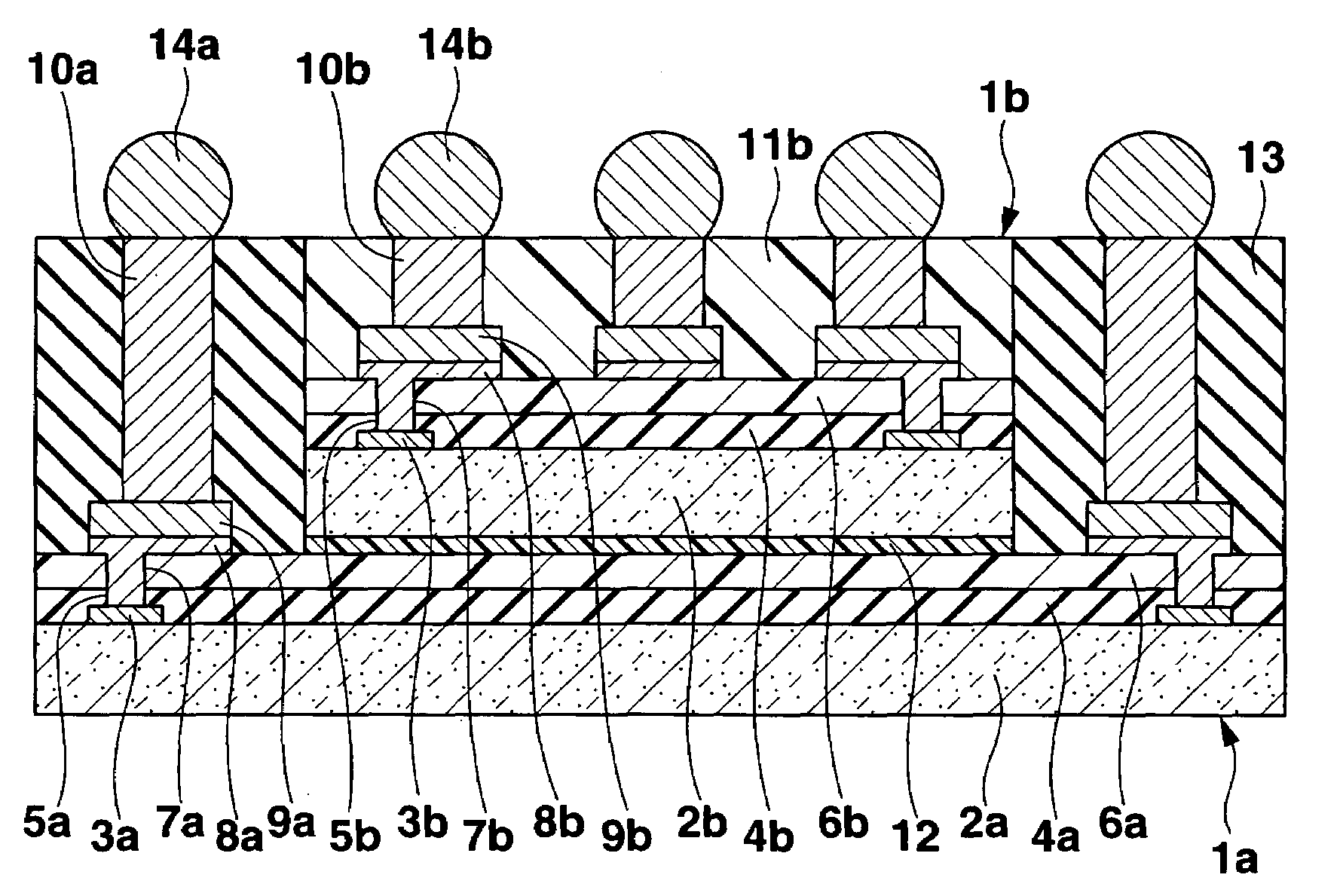

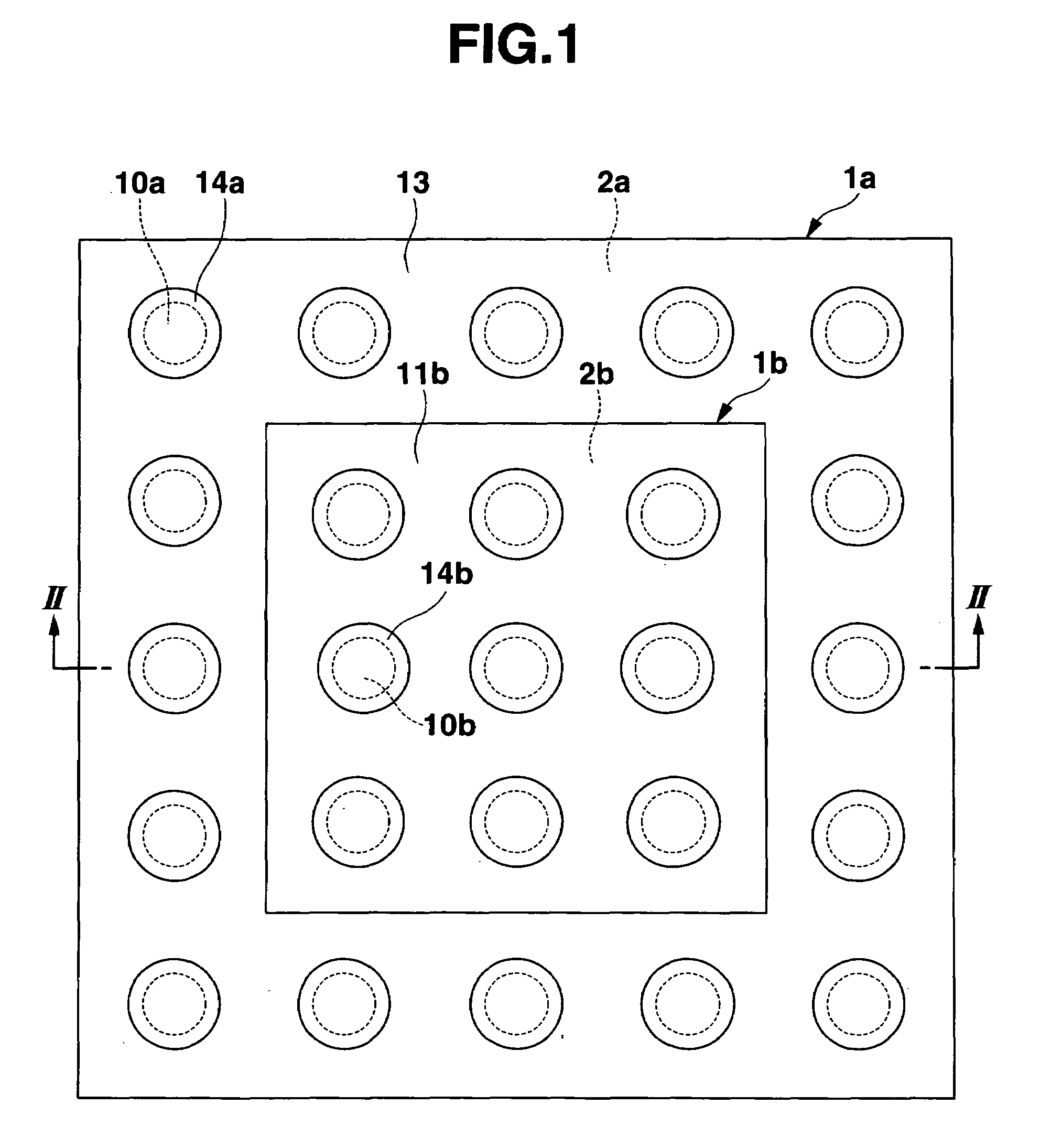

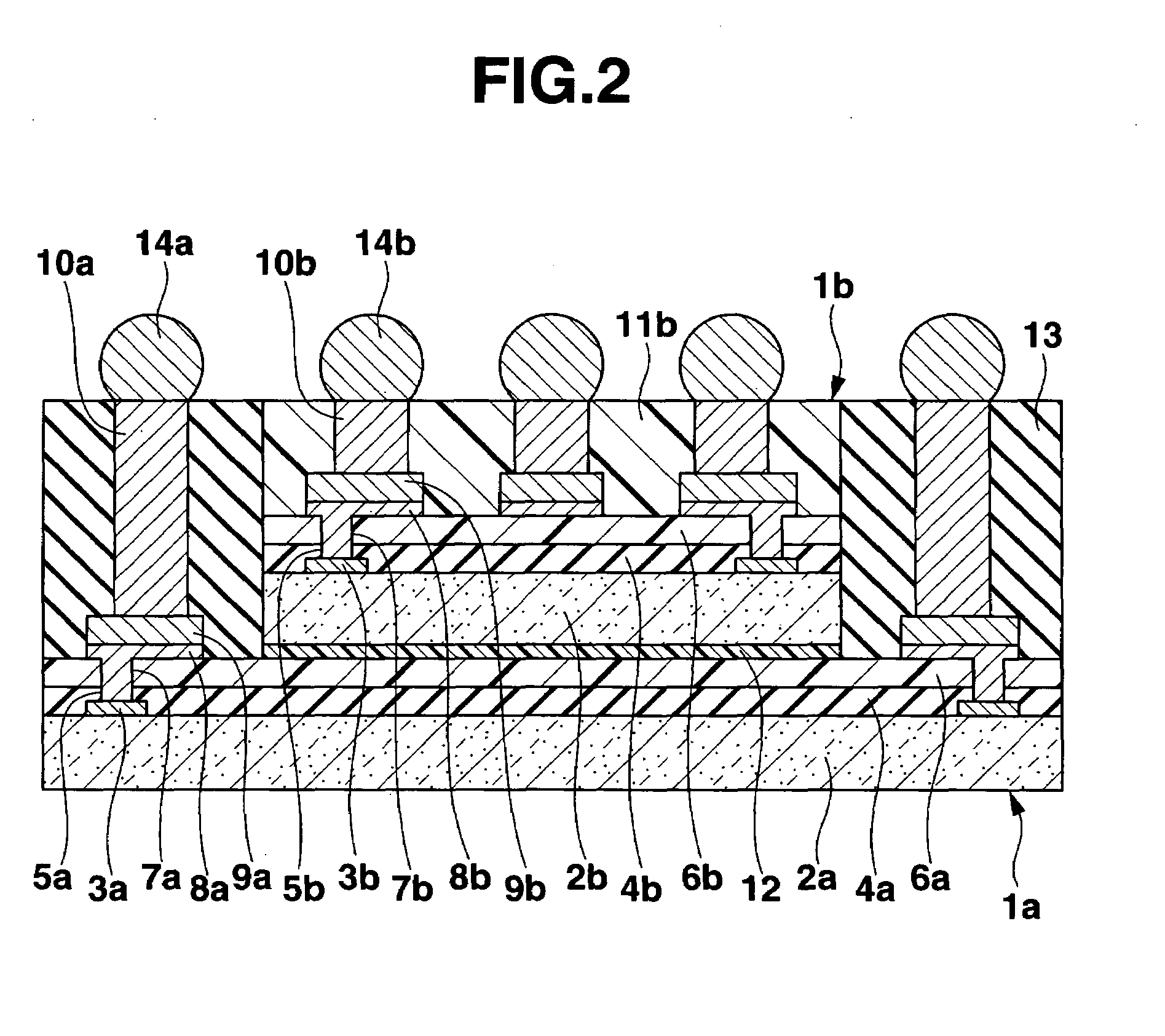

[0053]FIG. 1 is a plan view of a semiconductor device as a first embodiment of this invention, and FIG. 2 is a sectional view along the line II-II of FIG. 1. This semiconductor device includes a first planar square semiconductor construct 1a, and a second planar square semiconductor construct 1b stacked on the first semiconductor construct 1a. The first and second semiconductor constructs 1aand 1b are different in a planar-size but are much the substantially same in basic configuration, and are so-called chip size packages (CSPs) in general.

[0054]The first and second semiconductor constructs 1aand 1b respectively include planar square silicon substrates (semiconductor substrates) 2a and 2b. The planar-size of the second silicon substrate 2b is somewhat smaller than the planar-size of the first silicon substrate 2a. Integrated circuits (not shown) having a predetermined function are provided on the upper surfaces of the silicon substrates 2a and 2b, and a plurality of first and secon...

second embodiment

[0074]FIG. 12 is a sectional view of a semiconductor device as a second embodiment of this invention. This semiconductor device is different from the semiconductor device shown in FIG. 2 in that a semiconductor construct having no second sealing film 11b is used in a second semiconductor construct 1b, and in that an insulating film 13 is directly provided on the upper surface of a protective film 6b including a second wiring line 9b so that the upper surface of this insulating film 13 is flush with the upper surfaces of second columnar or bump electrodes 10b.

[0075]Next, one example of a method of manufacturing this semiconductor device will be described. First, after the step shown in FIG. 6, adhesive bonding layers 12 fixedly attached to the lower surfaces of silicon substrates 2b of a plurality of semiconductor constructs 1b are adhesively bonded to the centers of the areas on the upper surface of a protective film 6a on a silicon substrate 2a in a wafer state where first semicon...

third embodiment

[0077]FIG. 15 is a sectional view of a semiconductor device as a third embodiment of this invention. The great differences between this semiconductor device and the semiconductor device shown in FIG. 2 are that a semiconductor construct having a first sealing film 11a is used as a first semiconductor construct 1a, and that first and second upper layer wiring lines 17a and 17b, upper layer columnar or bump electrodes (third columnar electrodes) 18a and 18b, an overcoat film 19, solder balls 14a and 14b, etc. are provided on a second semiconductor construct 1b and an insulating film 13.

[0078]That is, the first semiconductor construct 1a has a structure in which the first sealing film 11a is provided on the upper surfaces of a protective film 6a and first wiring lines 9a so that the upper surface of the first sealing film 11a is flush with the upper surfaces of first columnar electrodes 10a. In this case, the height of the first columnar electrode 10a is somewhat smaller than the heigh...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com