Semiconductor wafer, apparatus and process for producing the semiconductor wafer

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

application examples

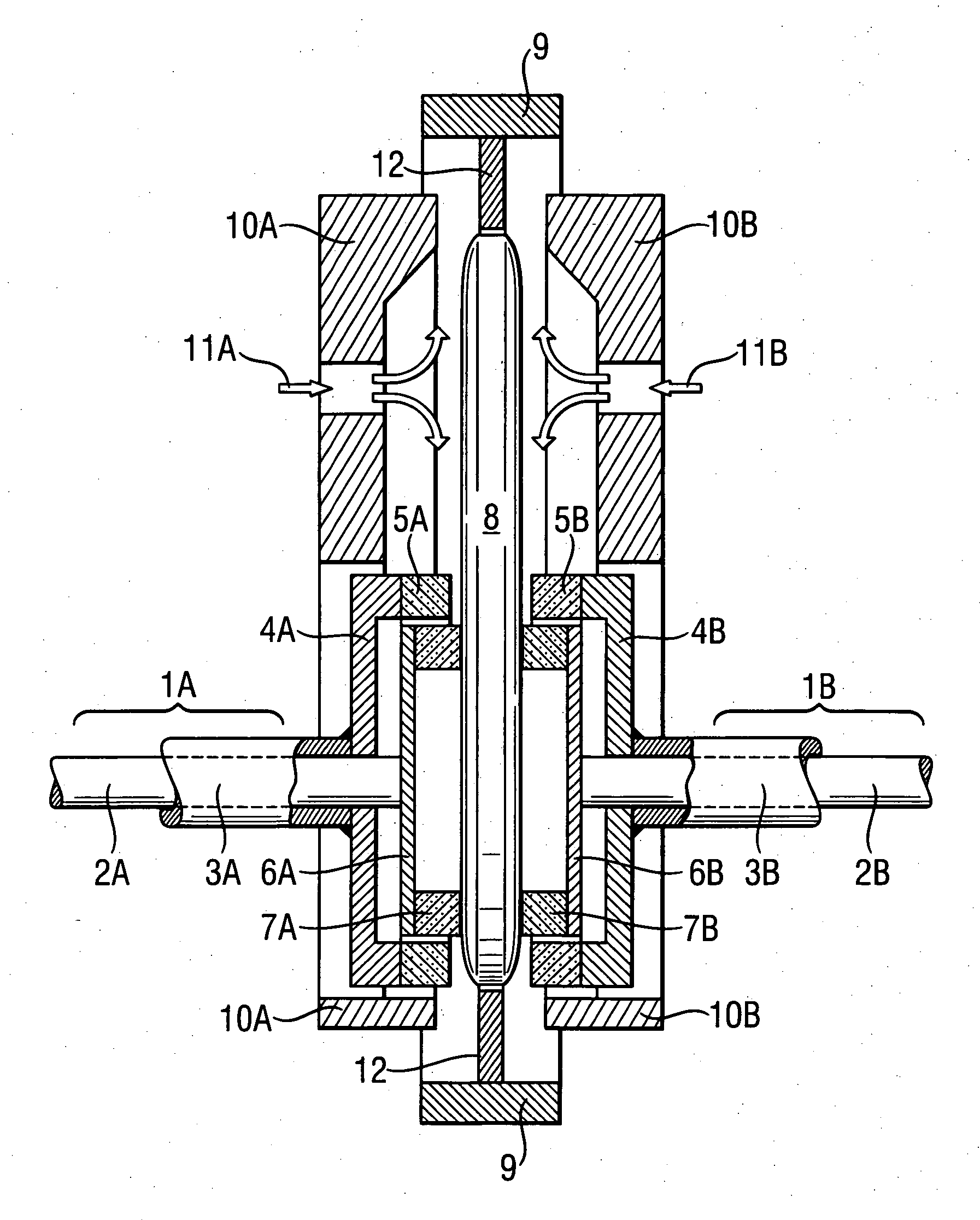

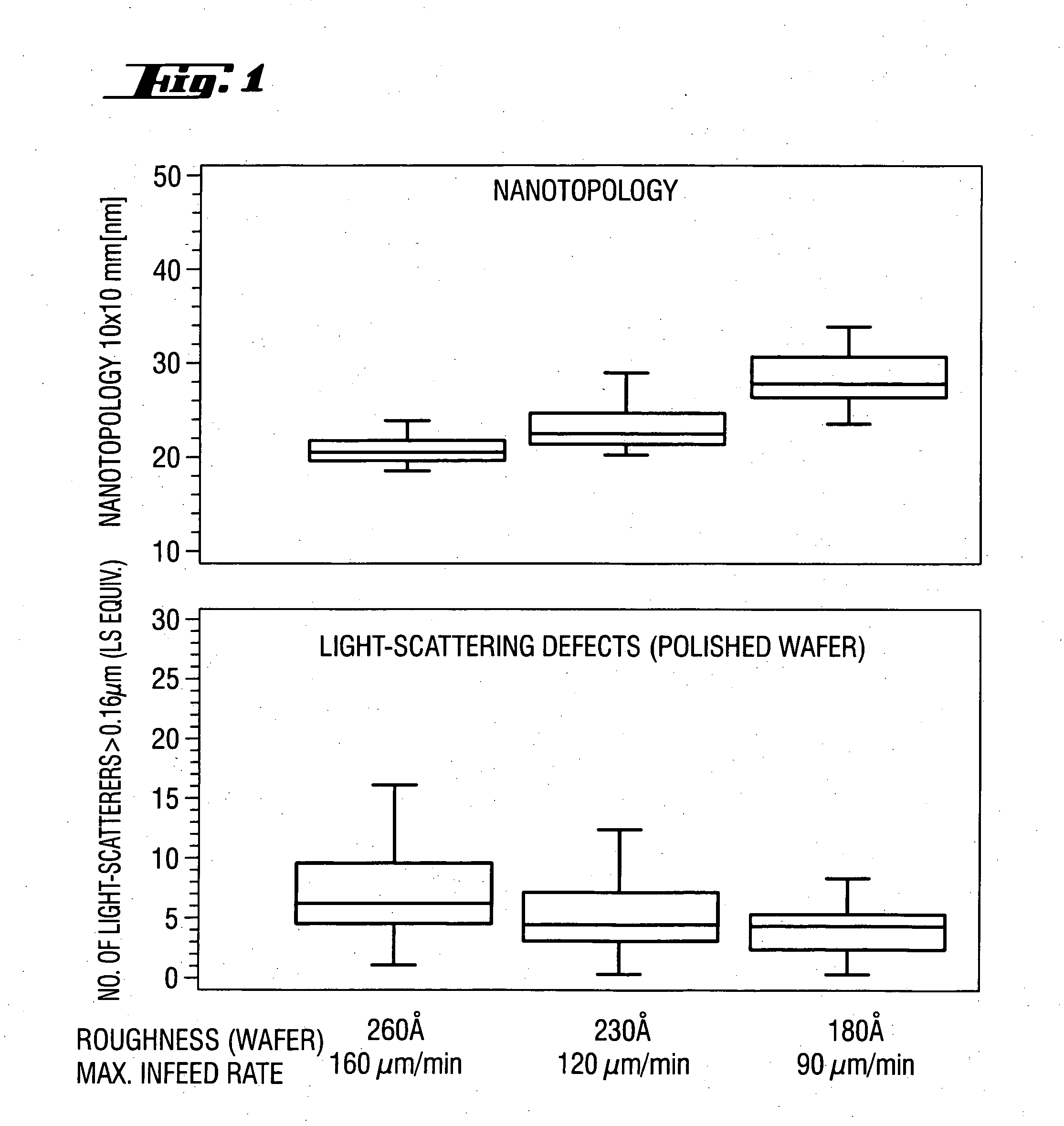

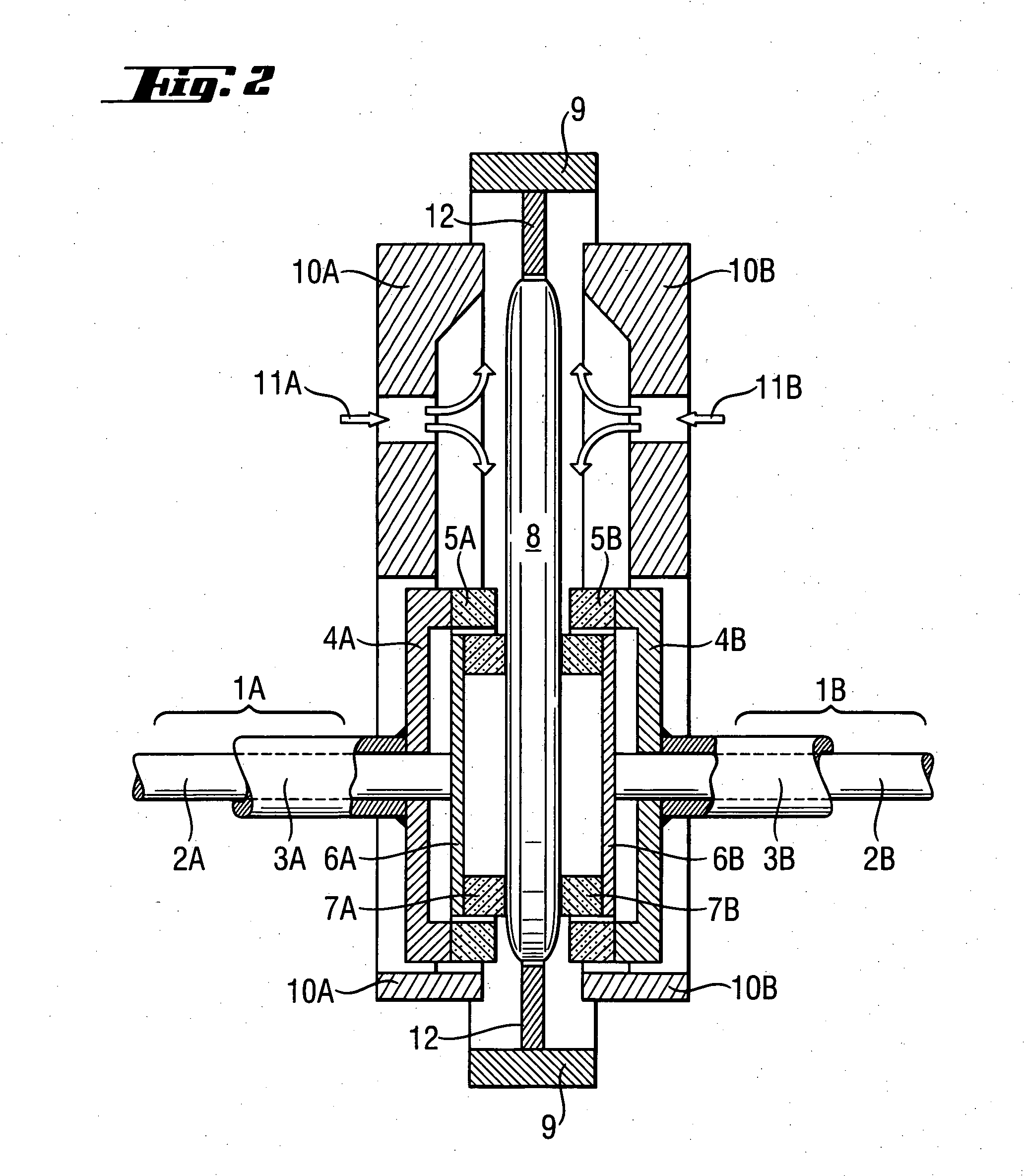

[0052] The following process parameters are among the preferred examples for an application of the DDDG process according to the invention:

[0053] In the case of rough-grinding, these parameters are as follows: a grinding wheel which is held by the inner or outer sub-spindle, has a grain size of 4-50 μm with diamond as the abrasive, ceramically or metallically bonded; grinding removal of 2×20 μm to 2×60 μm at a spindle rotational speed of 1000-12,000 rpm; a spindle infeed rate of 15-300 μm / min (based on both spindles); a semiconductor wafer rotational speed of 5-100 rpm; and cooling lubrication using 0.1-5 l / min of water. The result is a semiconductor wafer with rough-ground side faces having a roughness of 250-3000 Å RMS (using a profilometer with a 1-80 μm filter) and a total thickness variation TTV of 0.7-3 μm in the case of a process with coaxially arranged double spindles during rough-grinding.

[0054] In the case of finishing-grinding, the preferred parameters are: a grinding w...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Length | aaaaa | aaaaa |

| Length | aaaaa | aaaaa |

| Length | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com