Debugger apparatus and debugging method

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

embodiment 1

[0114] Embodiment 1

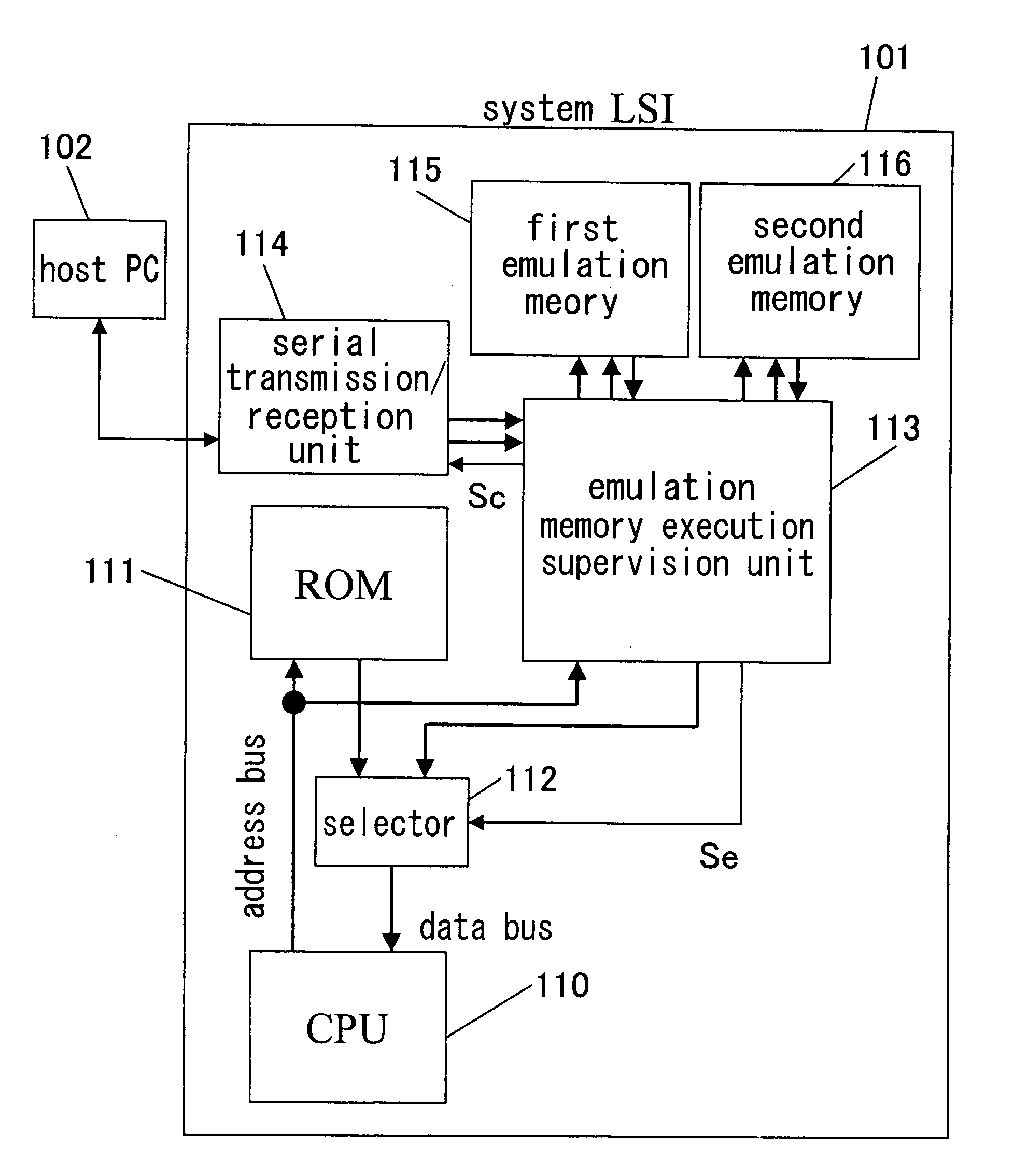

[0115] As shown in FIG. 1, a system LSI 101 comprises a CPU 110, ROM 111, selector 112, emulation memory execution supervision unit 113, serial transmission / reception unit 114, first emulation memory 115, and second emulation memory 116. Hereinafter, the emulation memory execution supervision unit is abbreviated to execution supervision unit, the serial transmission / reception unit to transmission / reception unit, the first emulation memory to first E-memory, and the second emulation memory to second E-memory. A host PC (hereinafter, abbreviated to host) 102 is a computer, wherein a debugger software capable of serial transmission and reception with respect to the transmission / reception unit 114 is installed.

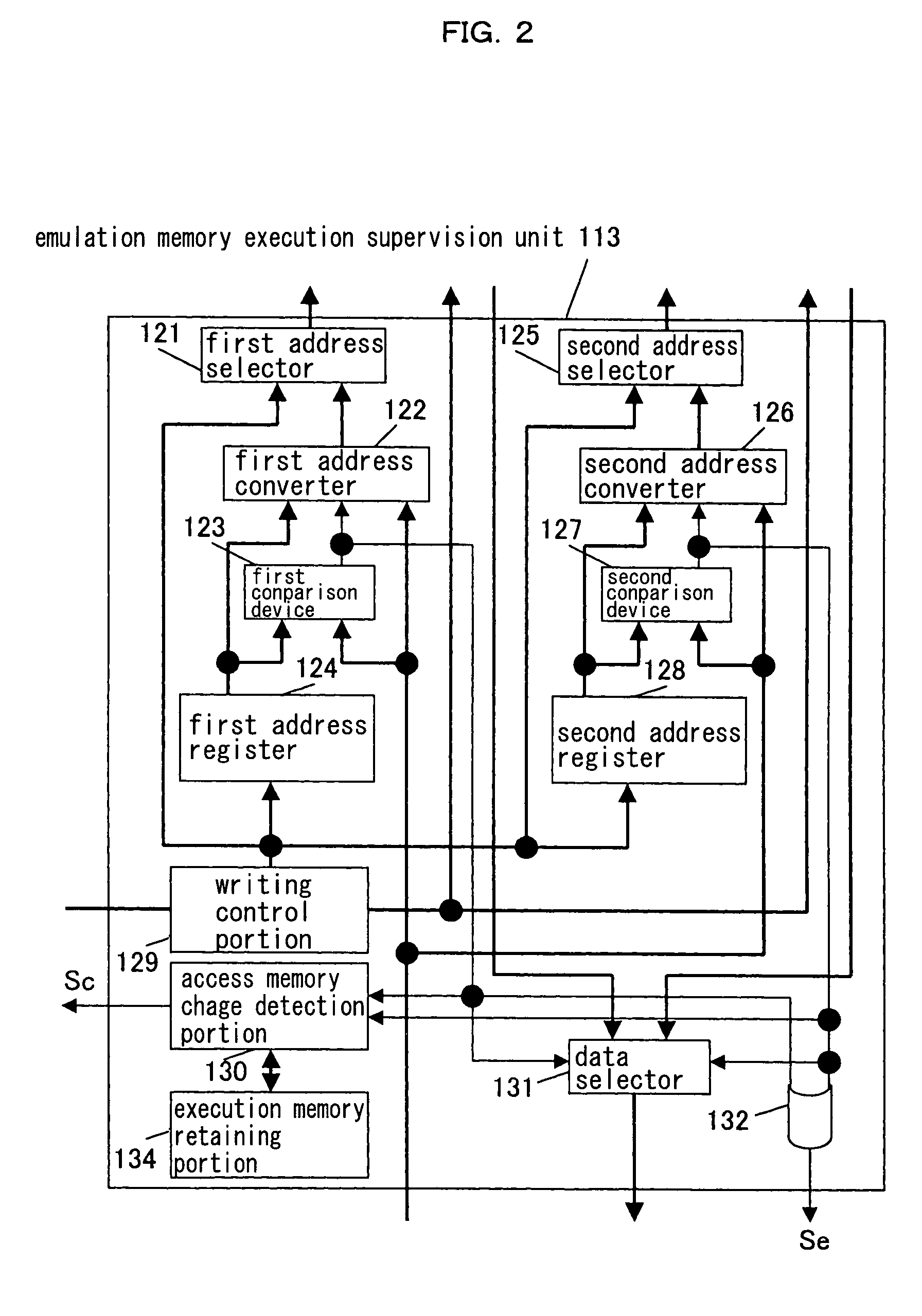

[0116] As shown in FIG. 2, the execution supervision unit 113 comprises a first address selector 121, a first address converter 122, first comparison device 123, first address register 124, second address selector 125, second address converter 126, second compa...

embodiment 2

[0147] Embodiment 2

[0148] In the embodiment 1, when there is an unconditional branch instruction prior to a final line of the memory capacity of an E-memory, the destination of the transferred instruction sequence is, without using the entire region of the E-memory, switched over to the other E-memory. In doing so, the overhead resulting from the traffic in transferring the instructions is generated. An embodiment 2 of the present invention deals with the inconvenience. In the embodiment 2, FIG. 1 is incorporated therein by reference.

[0149] As shown in FIG. 4, an E-memory execution supervision unit 113a comprises a first address / byte number register 136 in place of the first register 124 in the embodiment 1 (FIG. 2), and a second address / byte number register 138 in place of the second register 128 therein. In the description below, the first address / byte number register is abbreviated to first register, and the second address / byte number register to second register. The first and s...

embodiment 3

[0170] Embodiment 3

[0171] In the embodiment 2, even when the branch destination of the unconditional branch instruction of the instruction sequence 1 fits into the same E-memory, the instructions from the branch destination onwards are written in the other E-memory as the instruction sequence 2. Because of that, the overhead resulting from the transfer traffic increases. An embodiment 3 of the present invention deals with the inconvenience. In the embodiment 3, FIGS. 1 and 4 are incorporated therein by reference.

[0172]FIG. 6 shows instruction sequences including the unconditional branch instruction, the branch destination of which is present in the E-memory.

[0173] 1. Operation of Writing Instruction in E-Memory

[0174] The host traces the instructions, from the starting instruction, according to the execution sequence to thereby judge whether or not the branch destination corresponds to the memory region of the first E-memory 115 in the presence of the unconditional branch instruct...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com