Method of manufacturing a metal wiring in a semiconductor device

a manufacturing method and technology for semiconductor devices, applied in semiconductor devices, semiconductor/solid-state device details, electrical apparatus, etc., can solve the problems of underlying wiring alignment problem and the inevitable generation of upper wiring, and the above process still has severe problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

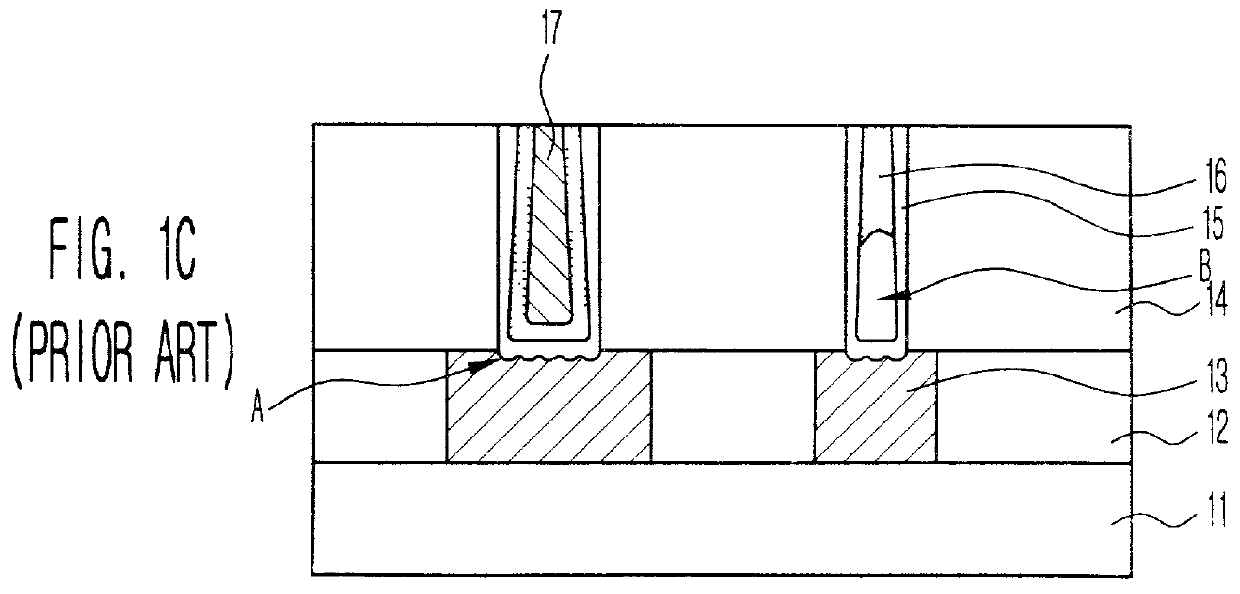

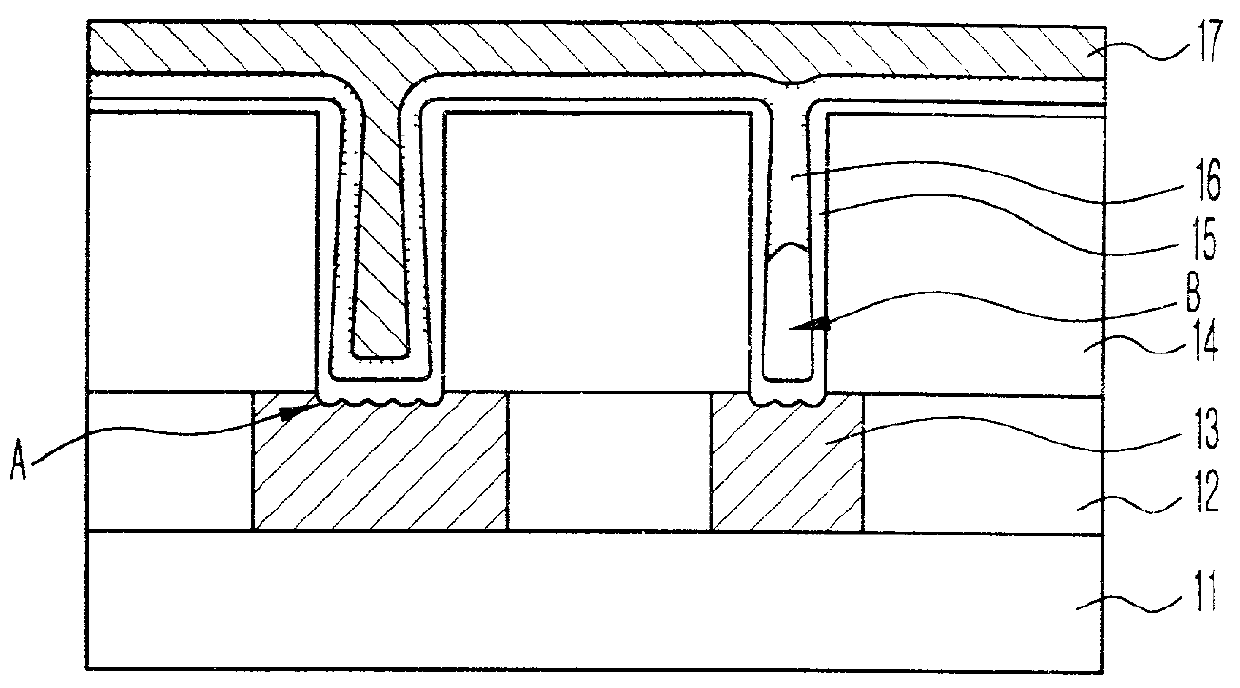

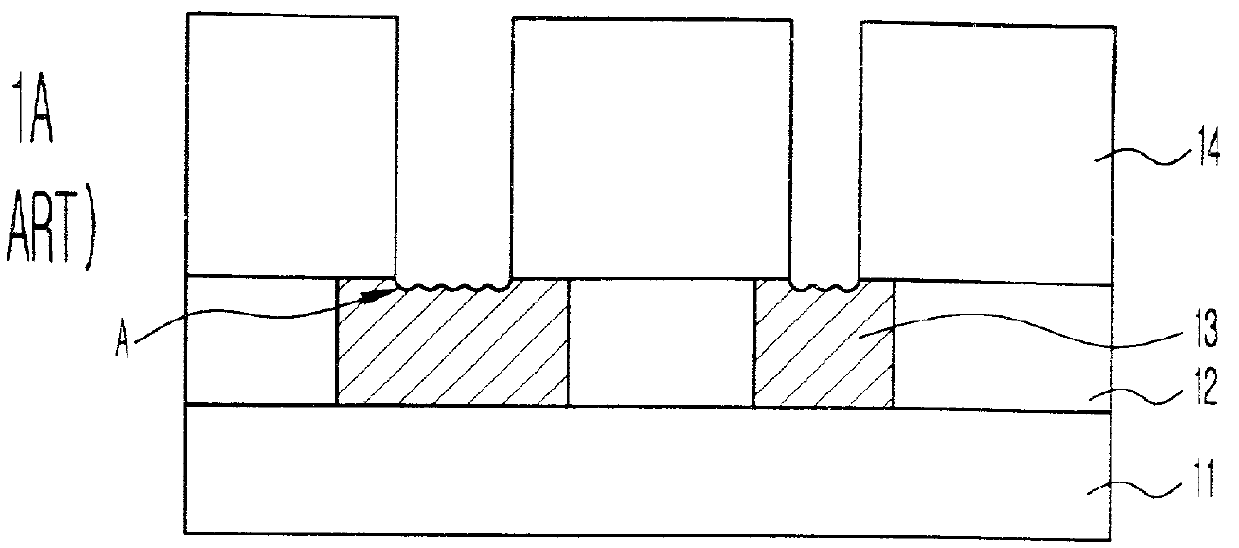

[0015] The disclosed methods will be described in detail by way of a preferred embodiment with reference to accompanying drawings. FIGS. 2A to 2D are cross-sectional views for explaining a method of manufacturing a metal wiring in a semiconductor device.

[0016] Referring now to FIG. 2A, a first insulating film 22 is formed on a semiconductor substrate 21 in which a given structure is formed. Then, after a given region of the first insulating film 22 is etched, a metal layer is formed on the etched region of the first insulating film 22 and is then patterned, thus forming an underlying metal wiring 23. After a photosensitive film 24 is formed with the same thickness to a desired height of the wiring, a portion in which an upper wiring will be formed is patterned to expose a portion of the underlying wiring 23. Then, a chemical enhancer 25, which is selectively adhered only to the exposed portion of the underlying metal wiring 23 without adhering to the photosensitive film 24, is depos...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com