Time-delay locking loop circuit

A technology of delay locked loop and locked loop, applied in the direction of electrical components, automatic power control, etc., can solve the problems affecting the response characteristics and indicators of the system, and achieve the effect of improving the fast response characteristics, suppressing the impact, and shortening the response time.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

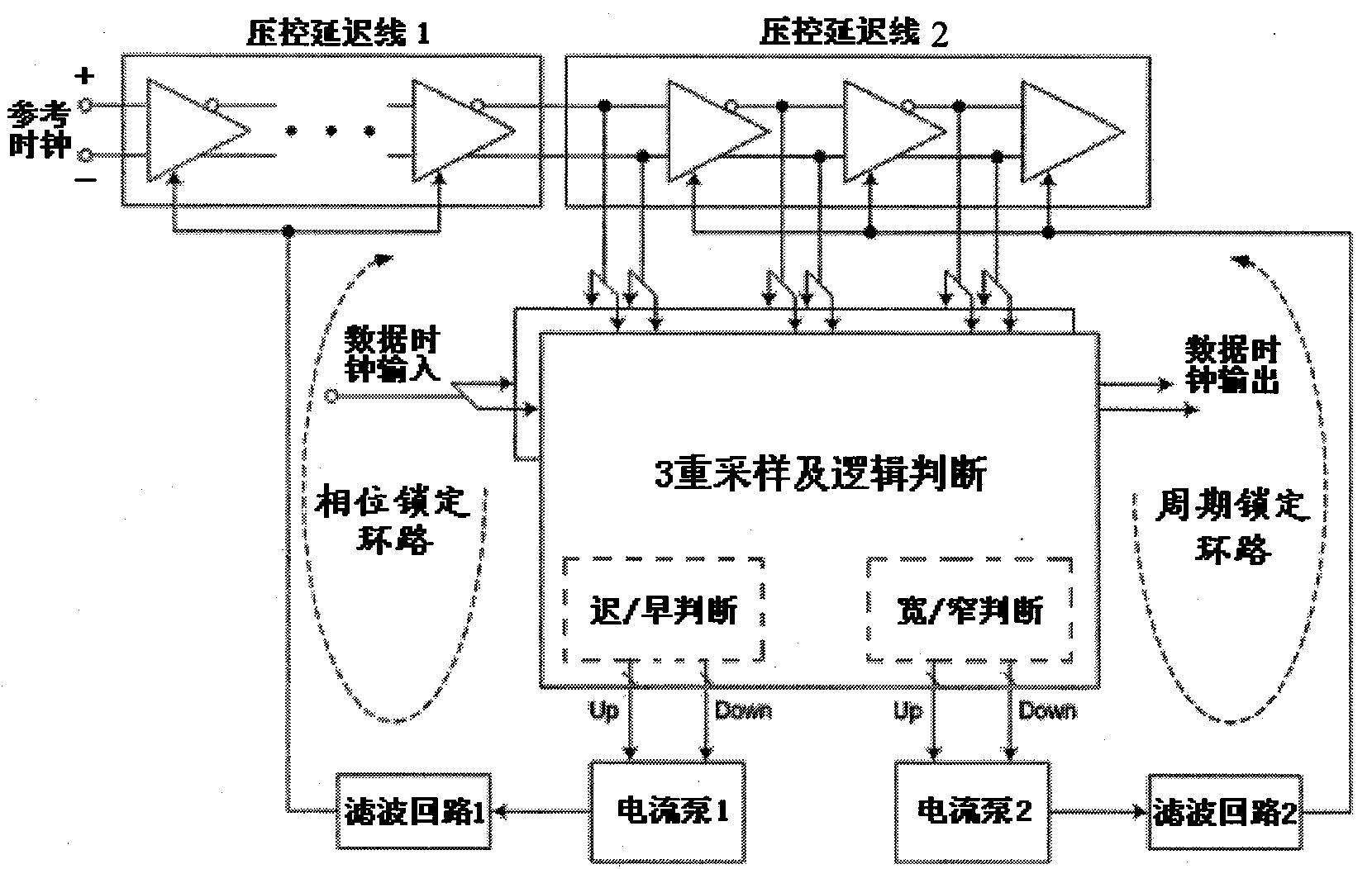

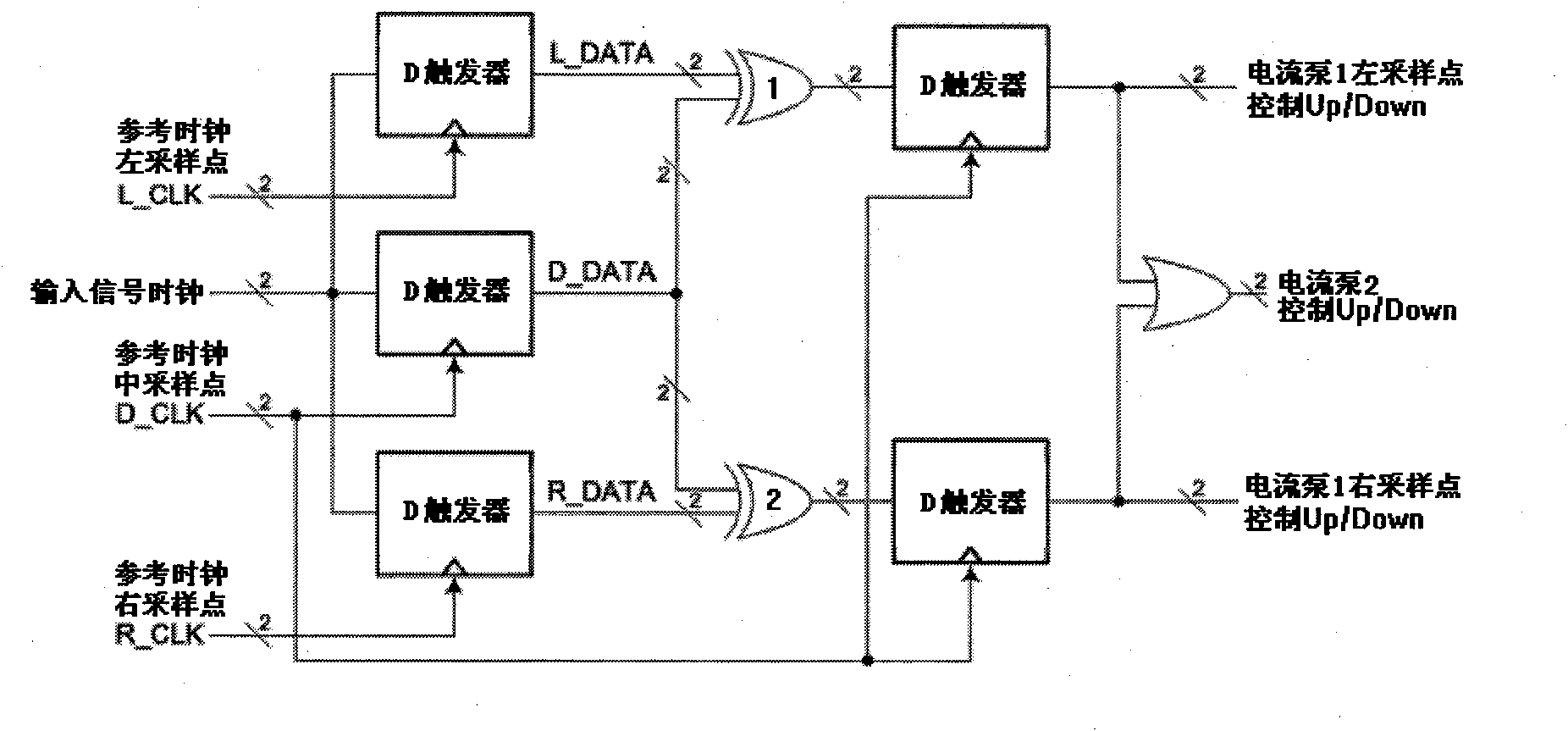

[0020] like image 3 As shown, it is a fully differential double-loop delay locked loop circuit of the present invention. It includes a signal phase-locked loop and a signal period-locked loop connected in series. In the signal path shown in the figure, the signal phase-locked loop includes triple signal sampling and logic judgment circuit, current pump 1, filter circuit 1 and voltage-controlled delay line circuit 1. The signal phase-locked loop first samples the signal through the triple sampling and logic judgment circuit, and judges whether the triple sampling point is in the same clock cycle, if the triple sampling point is not in the same signal clock, through the sooner or later logic ( Early / Late) circuit judges, generates UP / DOWN signals of the left and right sampling points to control the output voltage of the current pump 1, and changes the voltage-controlled delay line 1 through the filter circuit 1, so that the 3 re-sampling points return to the same clock.

[00...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com