Semiconductor chip buried base plate 3D construction and its manufacturing method

A semiconductor and chip technology, applied in the field of three-dimensional packaging structure and its manufacturing method, can solve the problems of unstable quality of the overall packaging structure, difficulty in filling insulating materials, easy generation of air bubbles, etc., and achieve good quality and product reliability, The effect of improving the good rate and saving the cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

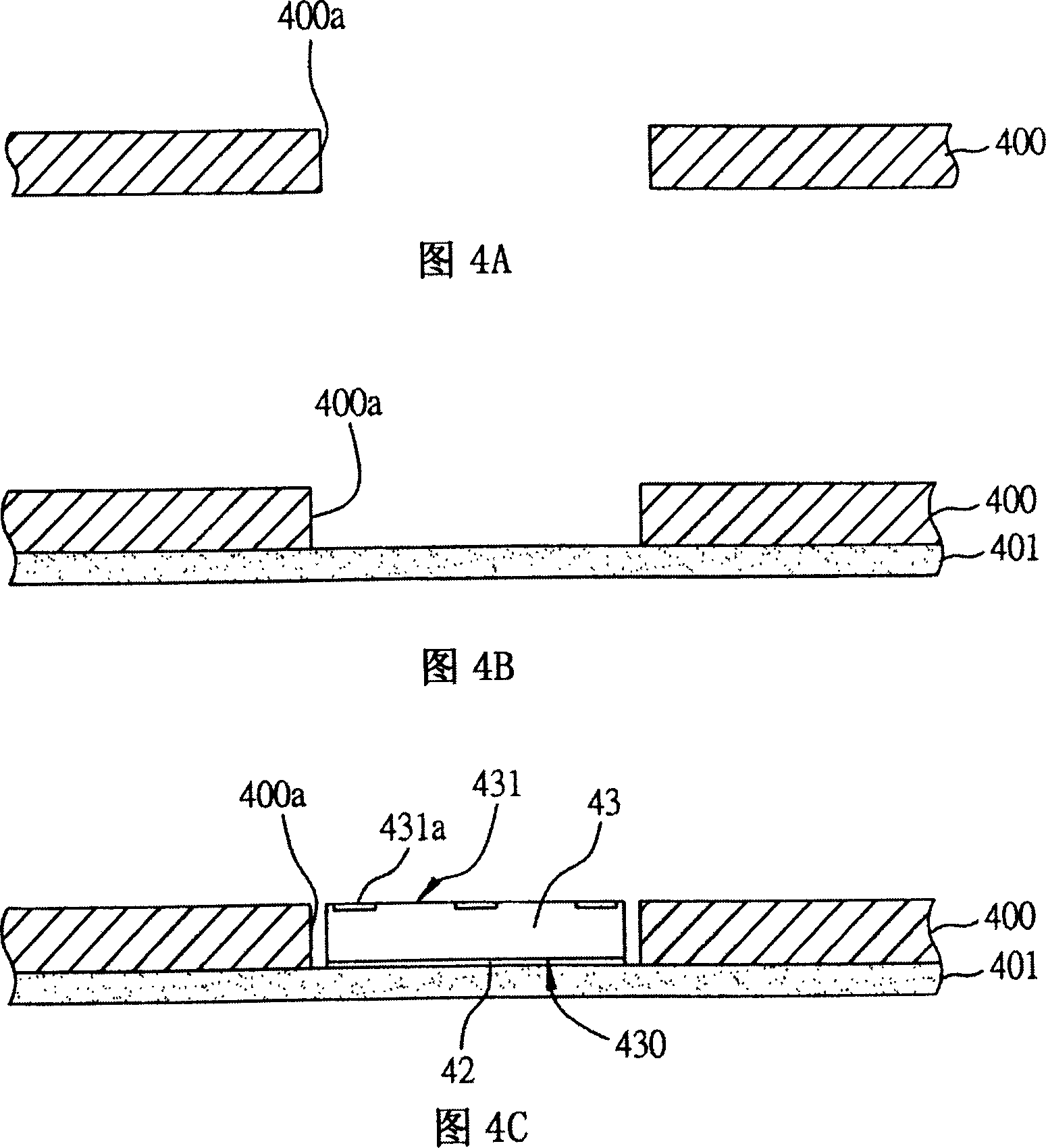

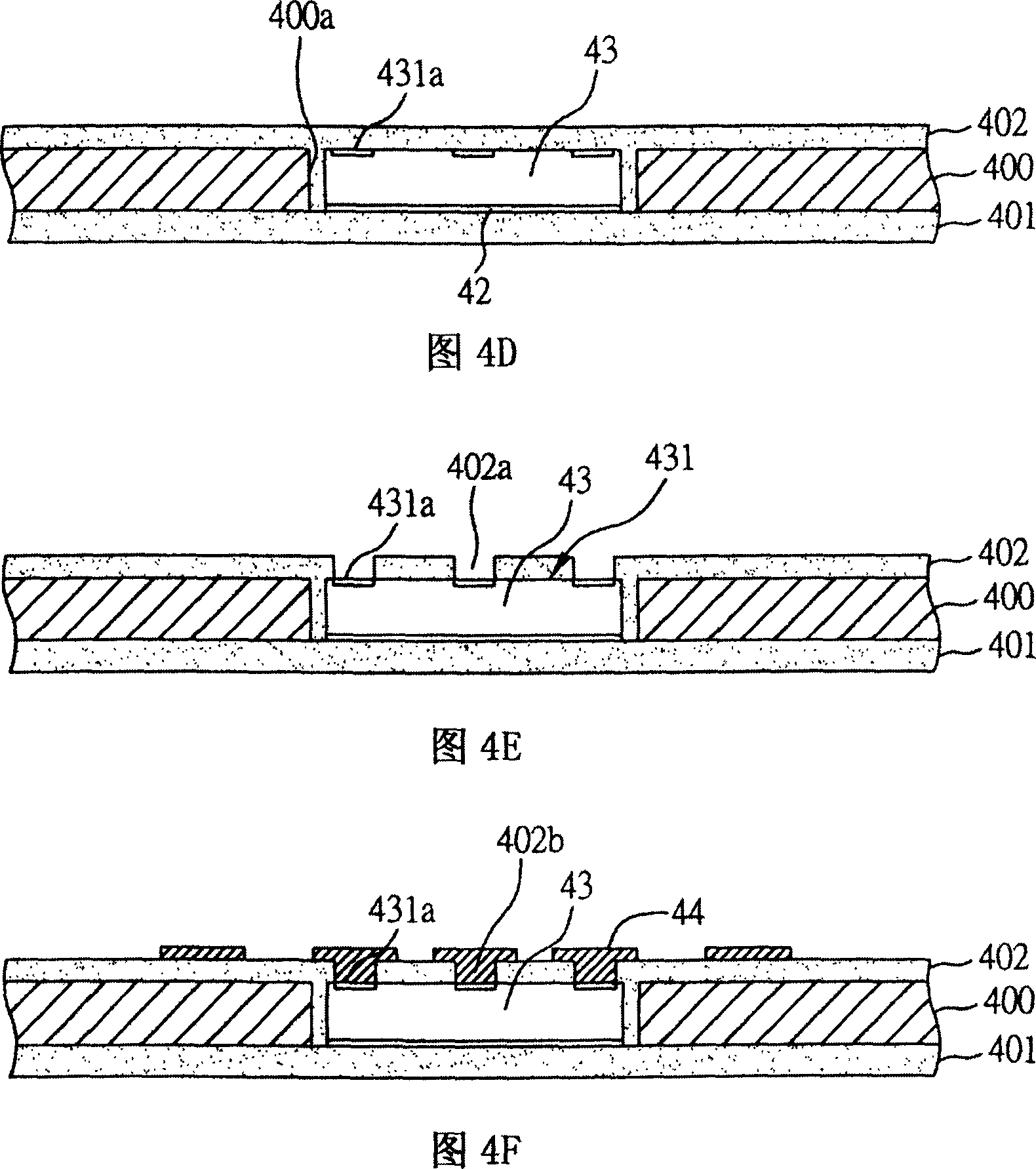

[0026] Please refer to FIGS. 4A to 4F , which are schematic cross-sectional views of Embodiment 1 of the manufacturing method of the semiconductor package structure of the present invention.

[0027] Referring to FIG. 4A , firstly, a carrier 400 having a through hole 400 a is provided. The carrier 400 can be an insulating core board, a metal plate or a circuit board with circuits, and the thickness of the carrier 400 can be determined as required.

[0028] Please refer to FIG. 4B , and then the carrier 400 is bonded on the first insulating layer 401 . The first insulating layer 401 can be prepreg (prepeg) or film (film) material, such as epoxy resin (epoxy resin), polyimide (polyimide), LCP, bismaleimide triazine ( BT, Bismaleimide triazine), ABF (Ajinomoto Build-up Film), polyphenylene ether (PPE), polytetrafluoroethylene (PTFE), benzocyclobutene (BCB, benzocylobutene), etc. The first insulating layer 401 is not fully cured insulating layer.

[0029]Referring to FIG. 4C , ...

Embodiment 2

[0035] Please refer to FIGS. 5A to 5H , which are schematic cross-sectional views of Embodiment 2 of the manufacturing method of the semiconductor package structure of the present invention. Embodiment 2 of the semiconductor assembly structure and its manufacturing method of the present invention is similar to Embodiment 1, the main difference is that a heat dissipation blind hole connected to the non-circuit surface of the semiconductor chip is formed in the first insulating layer, and the heat dissipation blind hole is filled with heat dissipation The material and the heat conduction circuit layer connected to the circuit structure are connected to the outside, and it can further provide direct external connection with other heat dissipation devices, so as to further improve the heat dissipation effect of the semiconductor package structure.

[0036] Referring to FIG. 5A , firstly, a carrier 500 having a through hole 500 a is provided. The carrier 500 can be an insulating co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com