Semiconductor memory

A semiconductor and memory technology, applied in the field of semiconductor memory, can solve problems such as failure to meet specifications and increase power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0056] Hereinafter, preferred modes for implementing the present invention will be described with reference to the drawings.

[0057] "Semiconductor Memory Circuits"

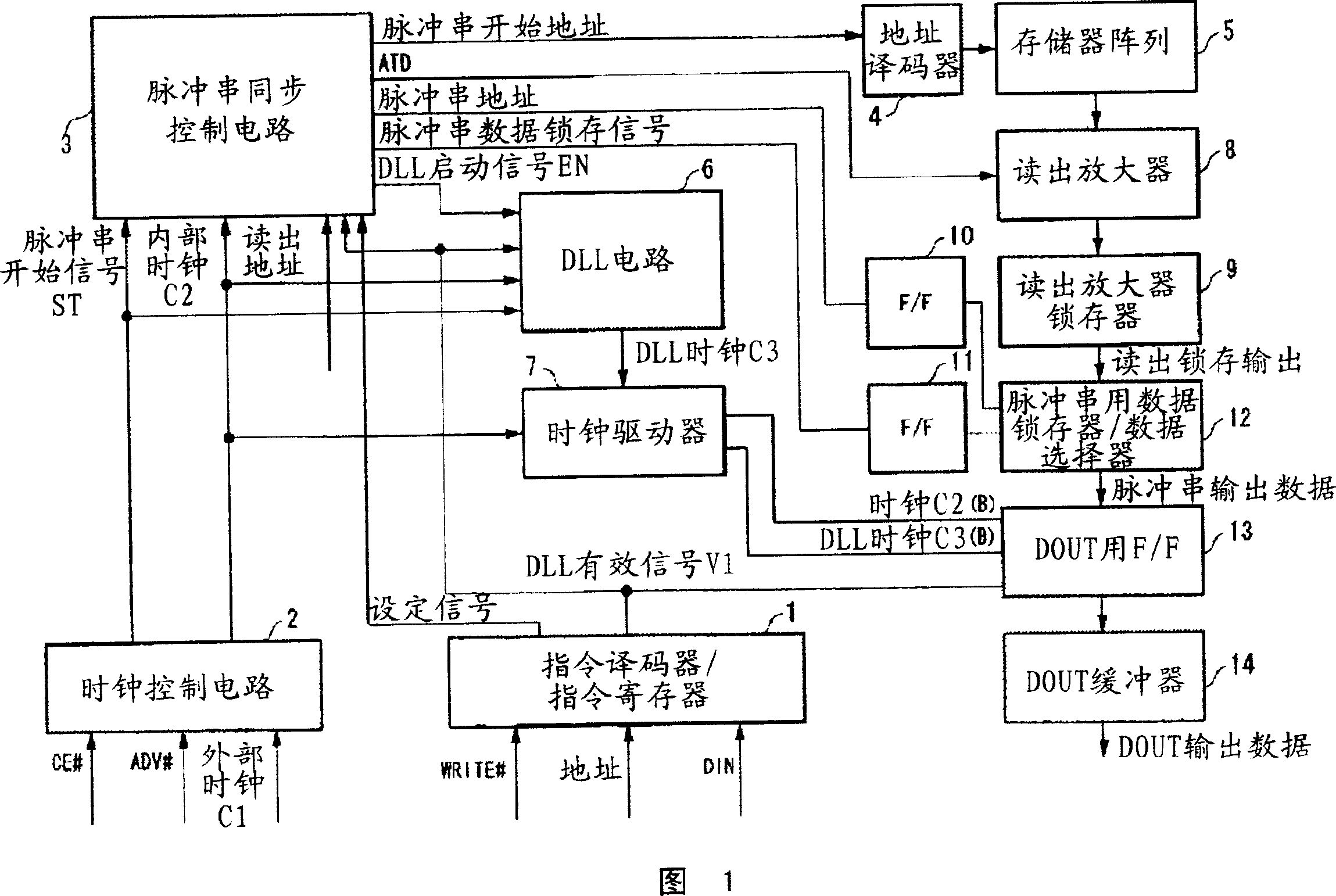

[0058] FIG. 1 is a diagram showing a configuration example (synchronous readout system) of a semiconductor memory in an embodiment of the present invention, and shows an example of a flash memory. In addition, "#" at the end of each signal indicates that it is valid at negative logic "L".

[0059] In Fig. 1, the instruction decoder / instruction register 1 decodes the address and DIN and determines the instruction, and uses the instruction write signal WRITE# to store the judgment result in the register. Also, set the type of burst mode, clock latency, and use / non-use of DLL. A DLL valid signal (a signal indicating use / non-use of DLL) V1 input based on a user command is output to the burst synchronization control circuit 3 , the DLL circuit 6 , and the flip-flop for DOUT (F / F for DOUT) 13 . In addition, a setti...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com