Nonvolatile memory unit, manufacturing method, and opertion method

A non-volatile, method-of-operation technology, applied in semiconductor/solid-state device manufacturing, electrical solid-state devices, semiconductor devices, etc., can solve problems such as inability to increase component integration and large size, achieve high electron injection efficiency and increase integration , Improve the effect of integration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

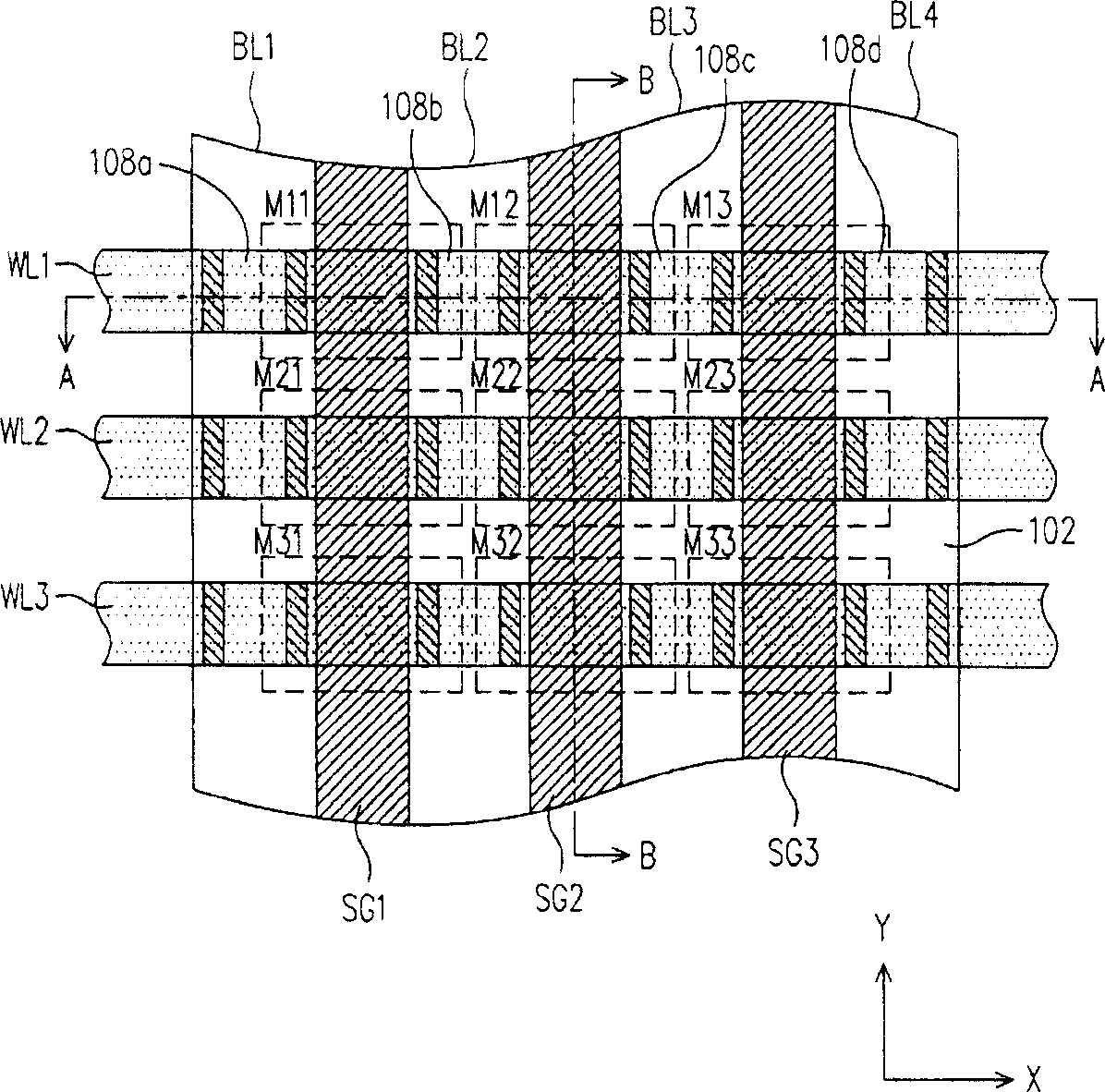

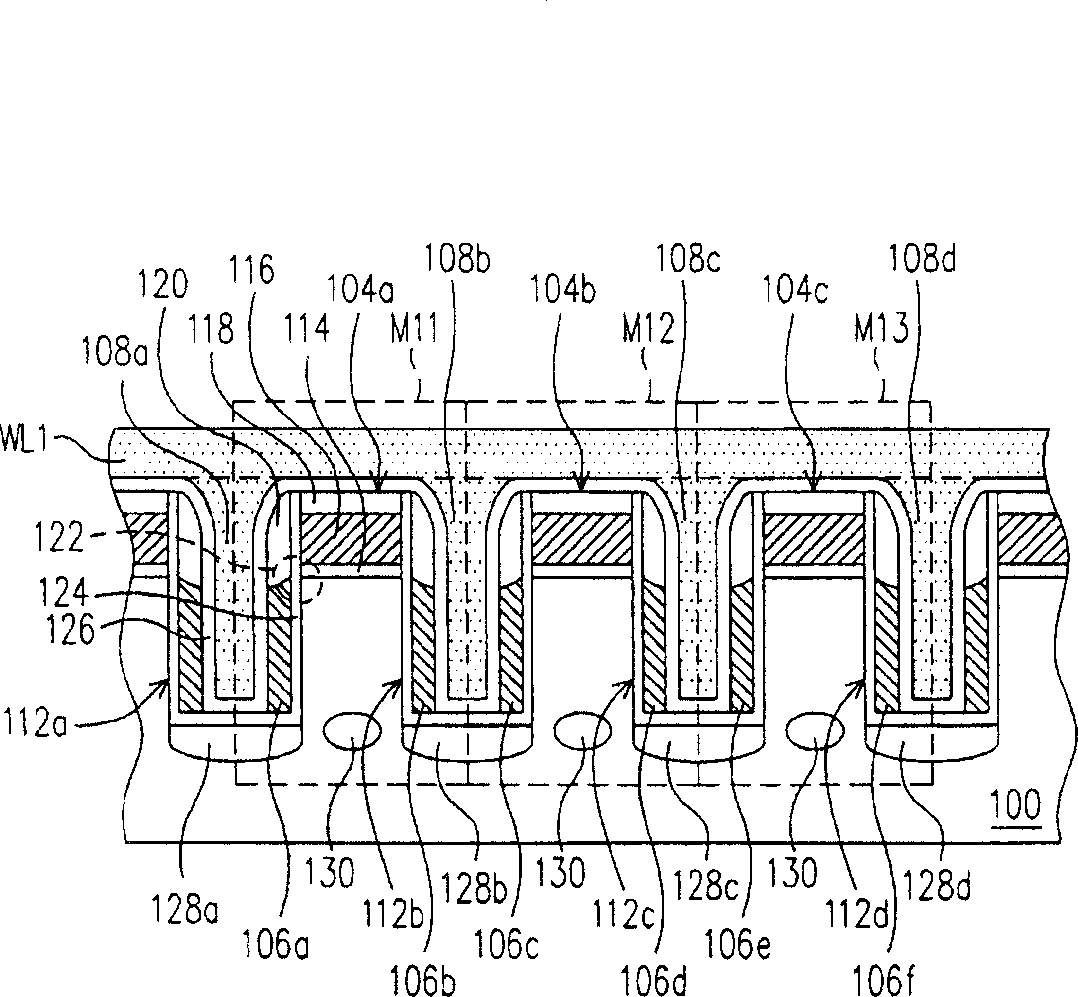

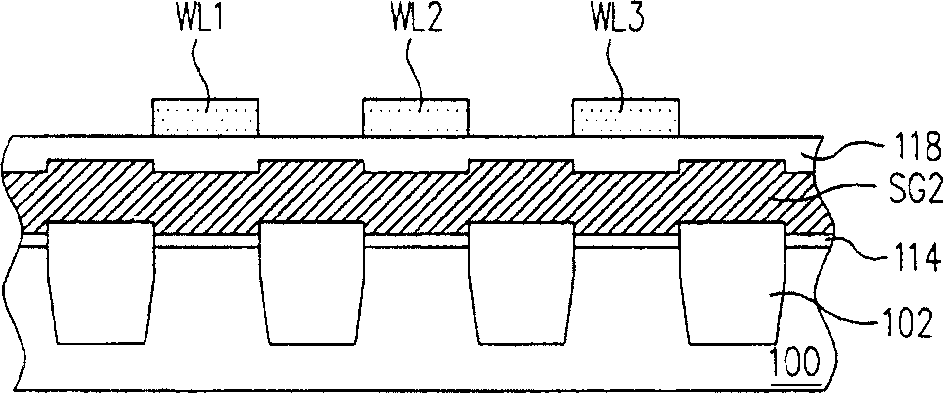

[0075] Figure 1A Shown is a top view of a preferred embodiment of the non-volatile memory of the present invention. Figure 1B for depicted as Figure 1A Structural cross-section along line A-A'. Figure 1C for depicted as Figure 1A The structural cross-section along the line B-B' in the middle.

[0076] Please refer to Figure 1A , the non-volatile memory array of the present invention includes a substrate 100, a plurality of memory cells M11-M33, a plurality of word lines WL1-WL3, a plurality of select gate lines SG1-SG3, and bit lines BL1-BL4.

[0077] The substrate 100 is, for example, a silicon substrate, and a plurality of device isolation structures 102 are disposed in the substrate 100 to define active regions. These component isolation structures 102 are arranged in parallel and extend towards the X direction

[0078] The memory cells M11-M33 are disposed on the substrate 100 and arranged in a row / column array. The multiple word lines WL1 - WL3 are respectively c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com