Display array, multi-layer complementary wire structure and mfg. method

A manufacturing method and display technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as time delay and display quality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

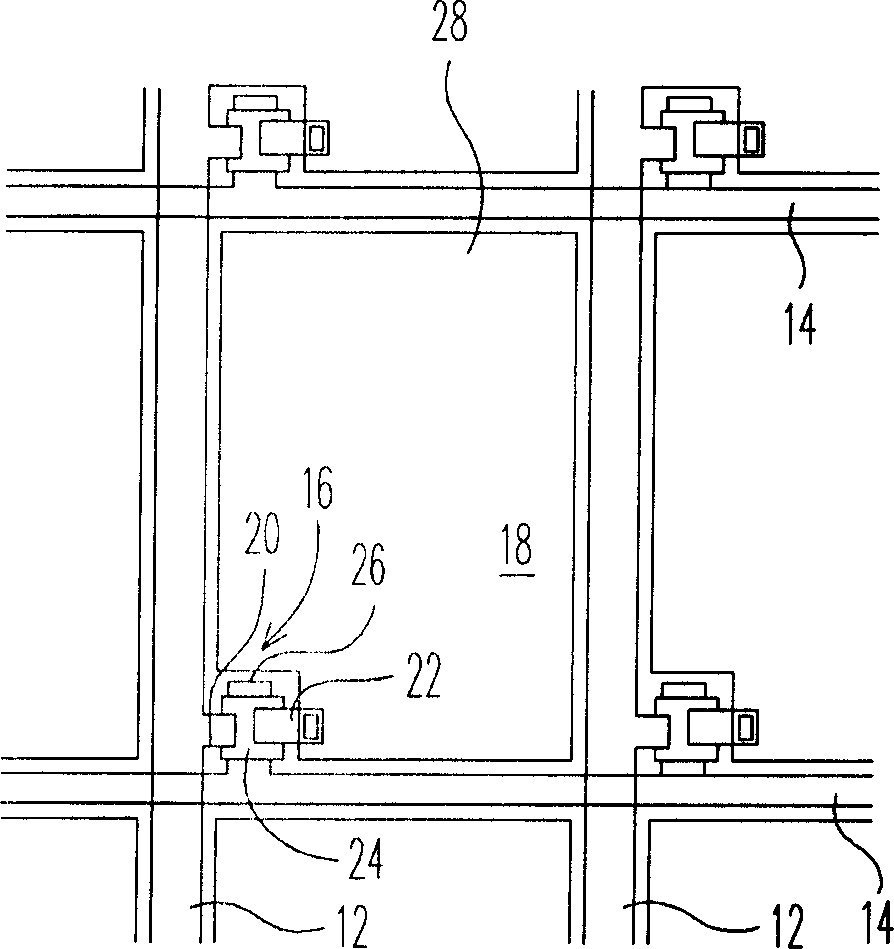

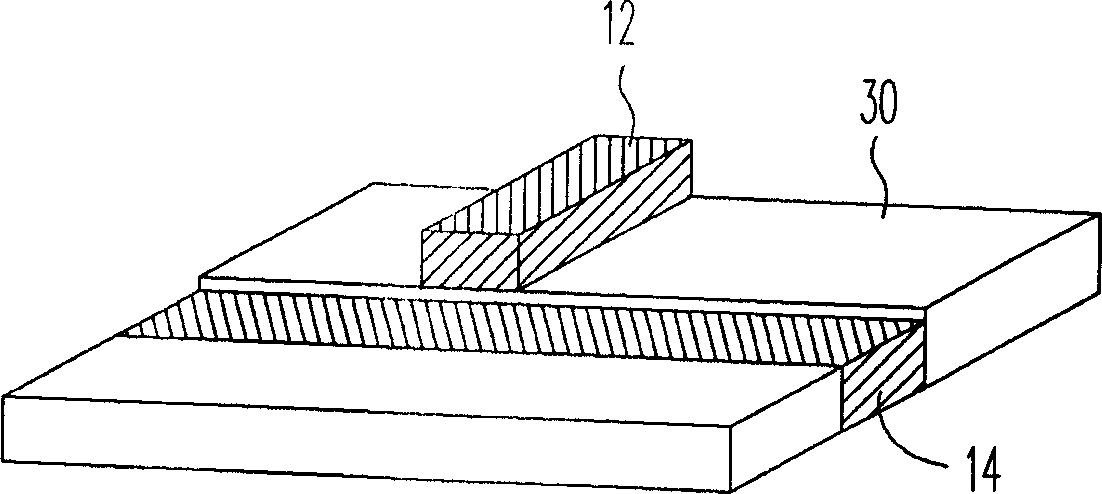

[0092] Figures 4A-4G It is a cross-sectional view of the manufacturing process of a conventional thin film transistor. First, please refer to Figure 4A The manufacturing method of the thin film transistor is to first form the metal layer M1 on the substrate 410. The substrate 410 can be a silicon substrate, a glass substrate or a plastic substrate, etc., and the metal layer can be a conductive metal material such as aluminum metal or copper metal. . Then use the first photolithography mask Mask-1 to pattern the metal layer M1 by means of photolithography and etching to form a gate (gate) 420 on the substrate 410 . Next, please refer to Figure 4B , forming a gate insulating layer, an active layer and a doped layer on the substrate 410 sequentially and comprehensively. The forming method is, for example, depositing (Deposition) an insulating layer (Insulating Layer) 430 , an amorphous silicon layer (Amorphous Silicon, “a-Si”) 440 and an ohmic contact layer (Ohmic Contact ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com