Semiconductor device and manufacturing method thereof

A manufacturing method and semiconductor technology, applied in the direction of semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve problems such as difficult to form thick films, filling metals, and reduced mechanical strength of semiconductor chips

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] According to the semiconductor device and its manufacturing method according to one aspect of the present invention, it is possible to obtain easily and at low cost the conductor layer insulated by the insulating resin layer with good adhesion to the inner wall surface in the through hole, which is suitable for lamination. A semiconductor device with high insulation reliability, such as a multi-chip package in which multiple semiconductor chips are mounted in layers.

[0034] Hereinafter, the form for carrying out this invention is demonstrated. In addition, in the following description, although embodiment is demonstrated based on drawings, these drawings are provided for illustration only, and this invention is not limited to these drawings.

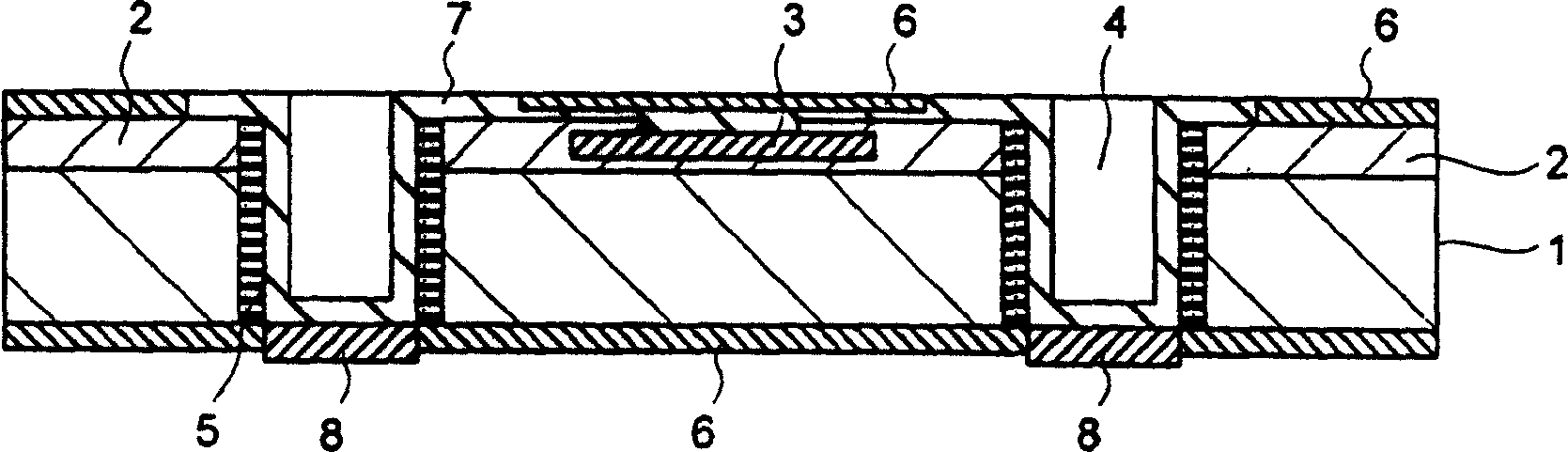

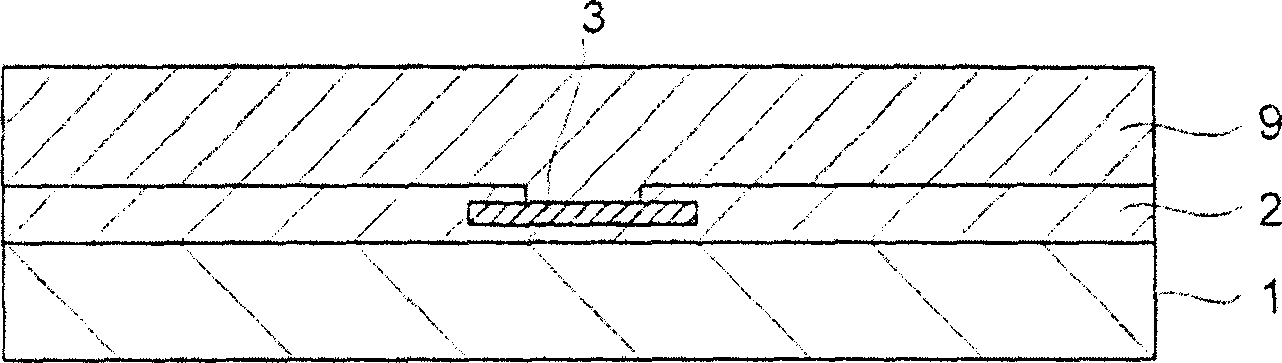

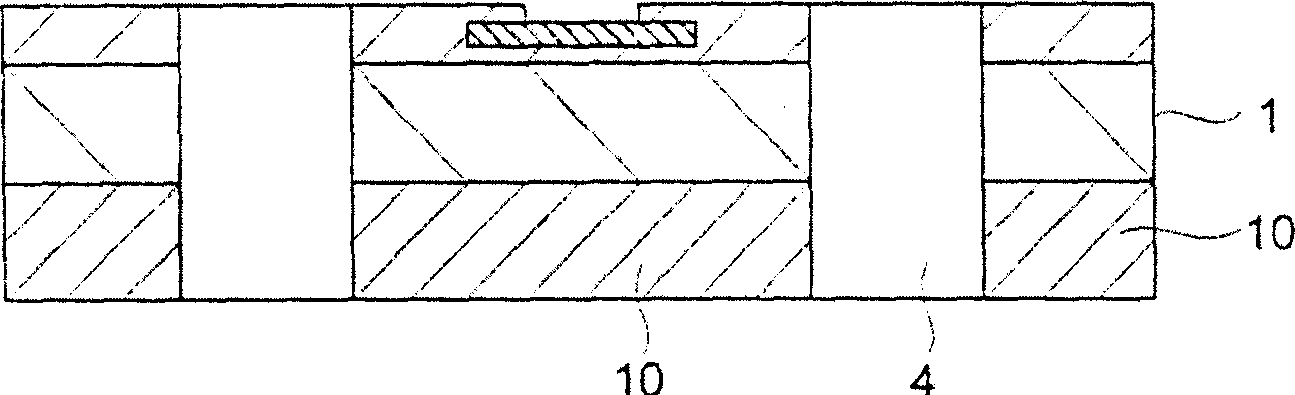

[0035] figure 1 The cross-sectional view of FIG. 1 shows the structure of the semiconductor device according to Embodiment 1 of the present invention. In the figure, reference numeral 1 denotes a semiconductor substrate such a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com