Signal processing device, signal processing method, delta-sigma modulation type fractional division PLL frequency synthesizer, radio communication device, delta-sigma modulation type D/A converter

A technology of a signal processing device and a frequency synthesizer, which is applied in the directions of analog-to-digital converters, physical parameter compensation/prevention, delta modulation, etc., can solve problems such as bad spurious signals, and achieve elimination of bad conditions, suppression of quantization noise, and elimination of quantization noise. The effect of spurious signals

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017]

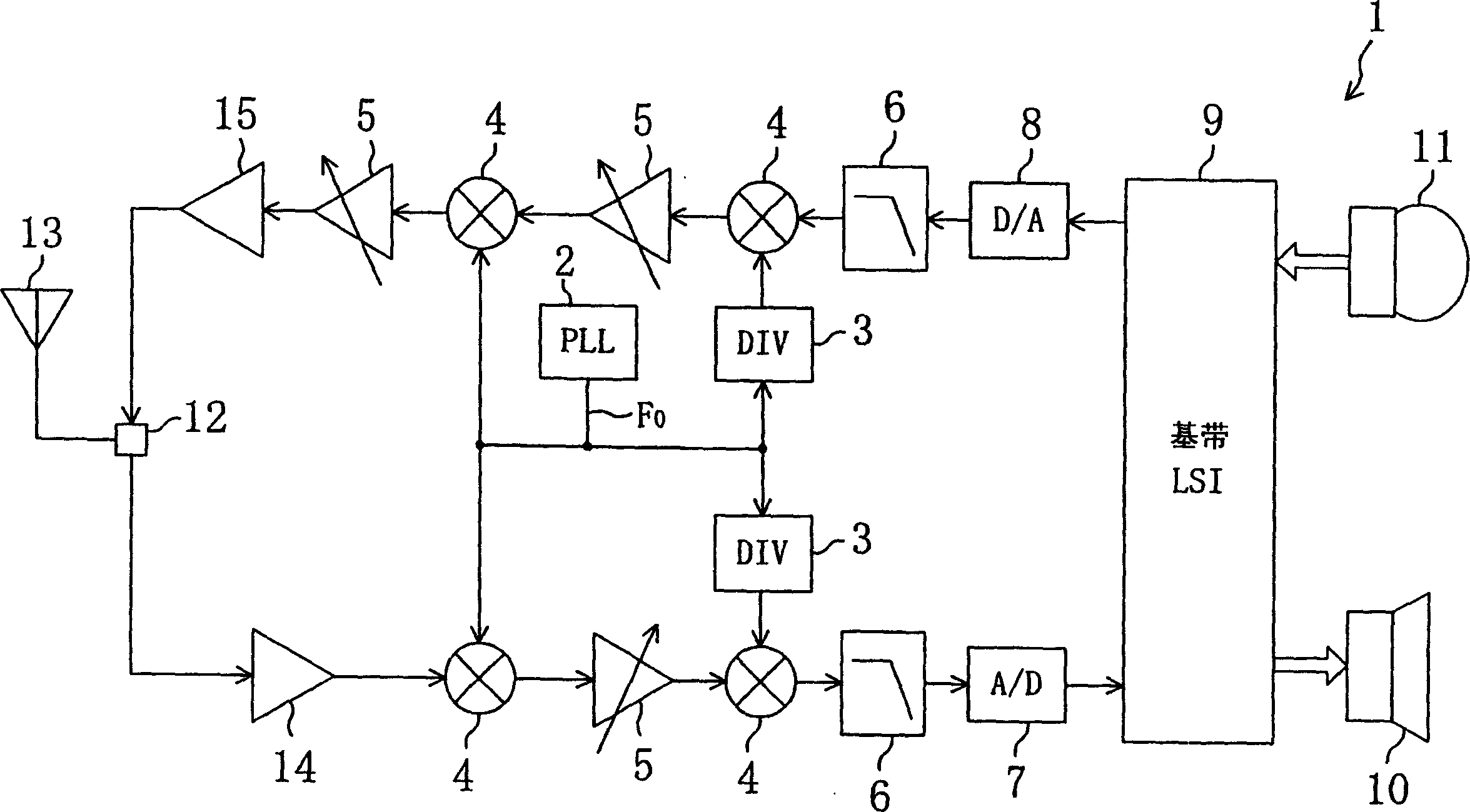

[0018] figure 1 It is a configuration block diagram of a mobile phone (wireless communication device) to which the ΔΣ modulation type fractional frequency division PLL frequency synthesizer of the present invention is applied. figure 1 The illustrated cellular phone has a ΔΣ modulation type fractional frequency division PLL frequency synthesizer 2, a frequency divider (DIV) 3, a modem (mixer) 4, a gain control amplifier (GCA) 5, a low pass filter (LPF ) 6, analog / digital (A / D) converter 7, digital / analog (D / A) converter 8, baseband LSI9, speaker 10, microphone 11, switch 12, antenna 13, low noise amplifier (LNA) 14 , Drive amplifier 15. f o Represents the output signal of the ΔΣ modulation type fractional frequency division PLL frequency synthesizer 2.

[0019]

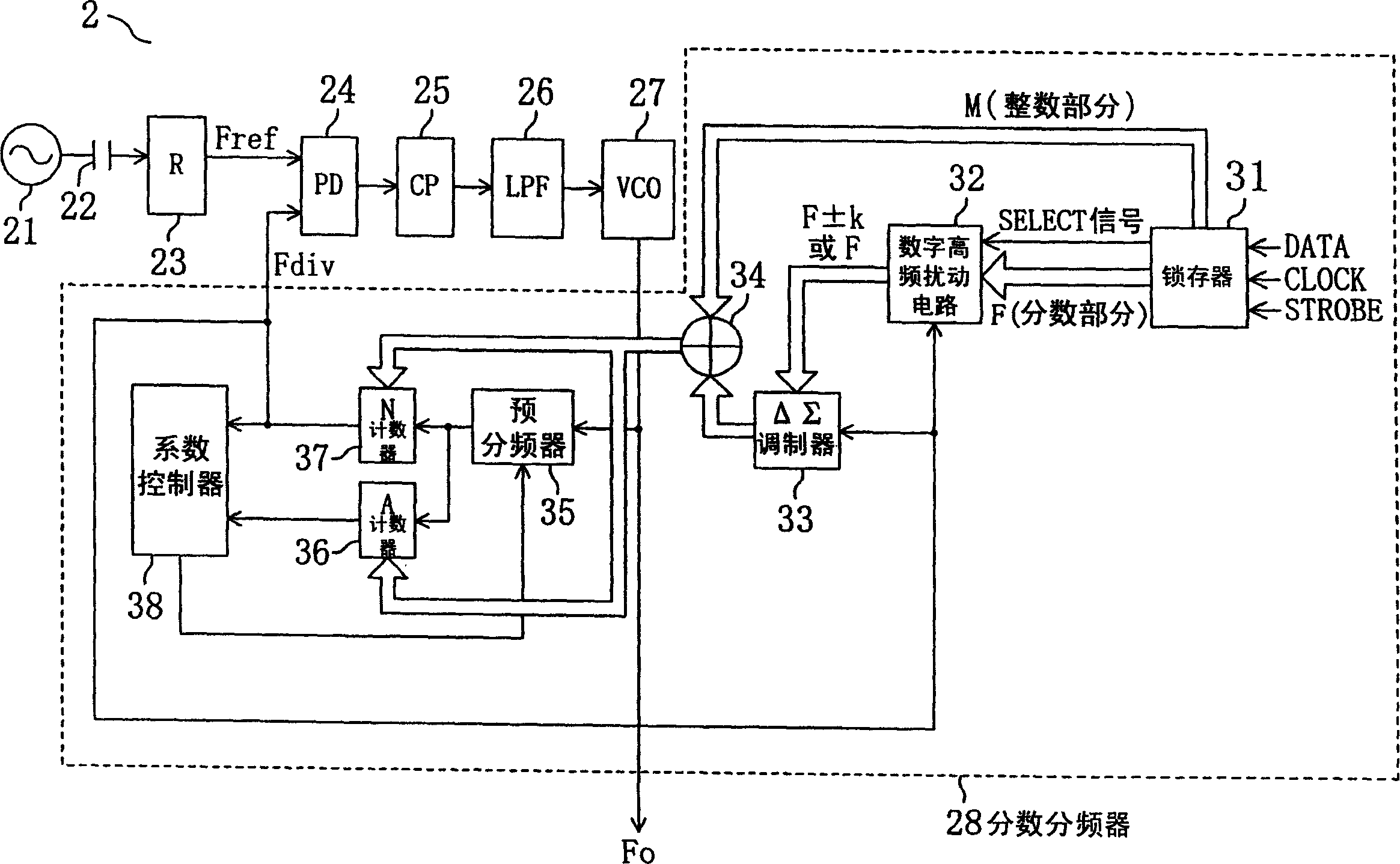

[0020] figure 2 yes means figure 1 The block diagram of the internal structure of the ΔΣ modulation type fractional frequency division PLL frequency synthesizer 2 is shown. refer to figure 2 , Th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com