Semiconductor memory device having advanced data strobe circuit

A data strobe, pulse circuit technology, applied in digital memory information, information storage, static memory and other directions, can solve the problem of short timing margin, not suitable for high-speed operation and so on

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] Hereinafter, a semiconductor memory device having an advanced data strobe circuit according to the present invention will be described in detail with reference to the accompanying drawings.

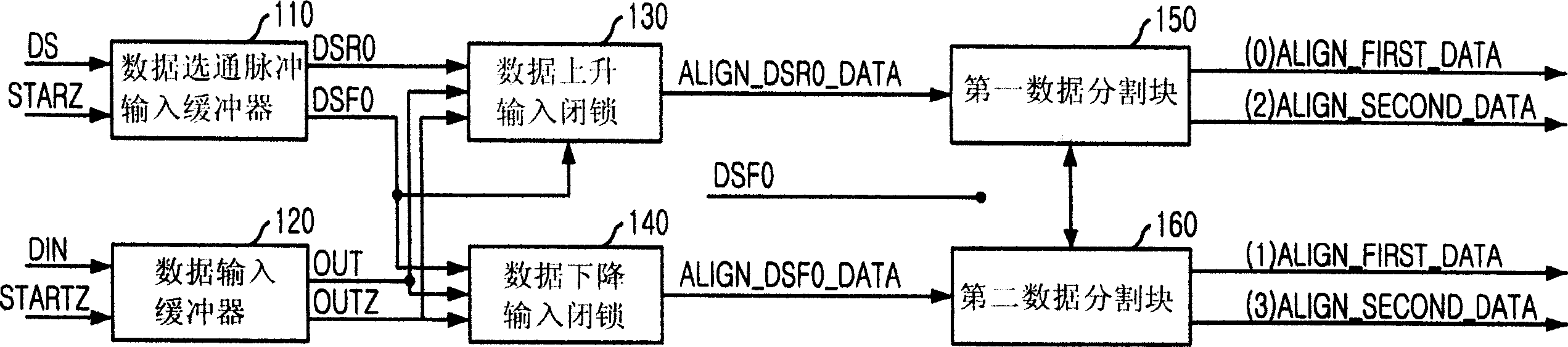

[0030] Figure 4 It is a block diagram of a data strobe circuit according to an embodiment of the present invention.

[0031] As shown in the figure, the data strobe circuit includes a data strobe buffer block 400, a data strobe division block 420, a data input buffer block 410, a blocking block with first to fourth blocking units 430 to 460, And a data alignment block having first to third alignment units 470 to 490.

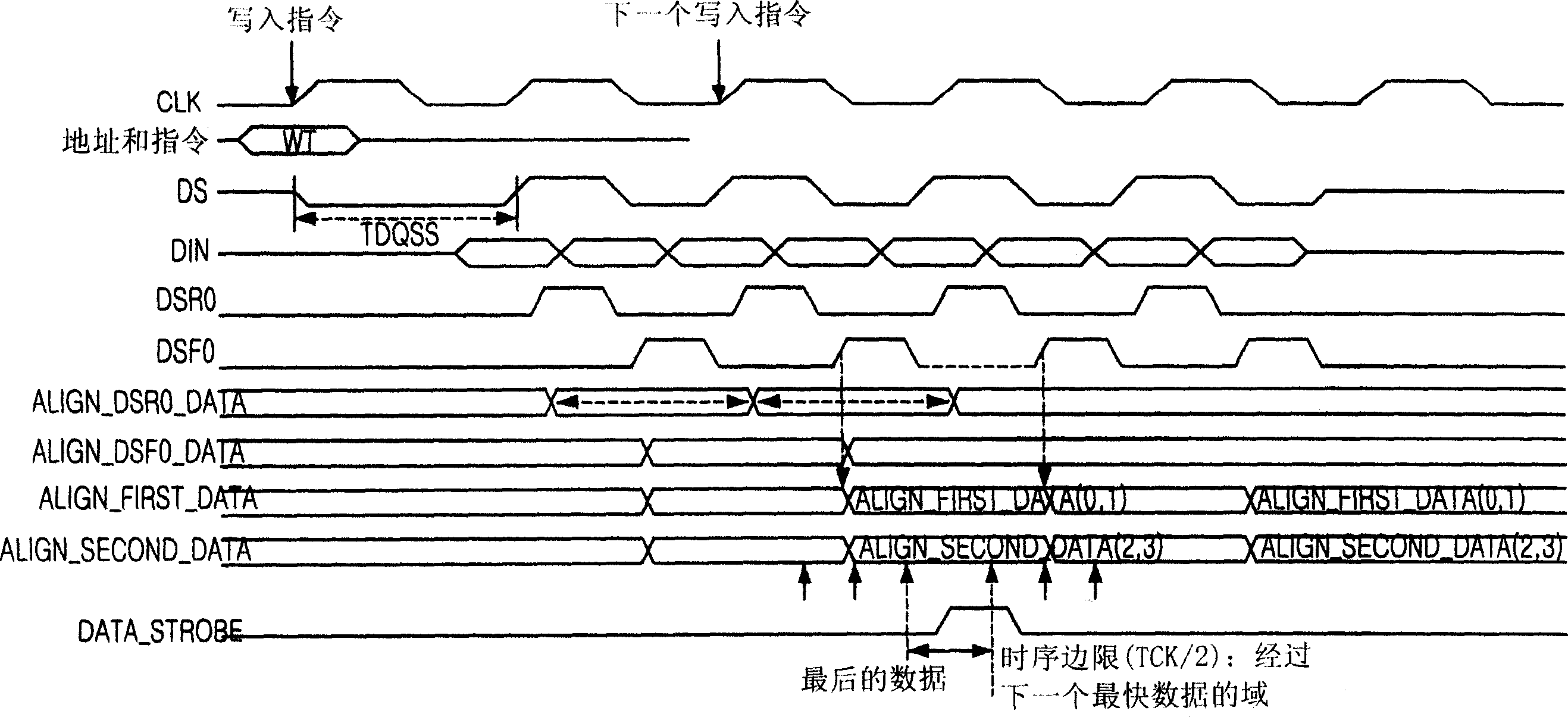

[0032] The data strobe buffer block 400 receives the data strobe signal DS, and then outputs a buffered data strobe signal DSBUF_OUT. The data input buffer block 410 receives input data DIN, and then outputs buffered input data DIN_OUT. The data strobe splitting block 420 receives the buffered data strobe signal DSBUF_OUT, and then generates first rising and falli...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com