Semiconductor device and mfg. method thereof

A manufacturing method and semiconductor technology, applied in the fields of semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of reduced electron mobility, reduced transistor driving force, and crystallization of semiconductor substrates. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

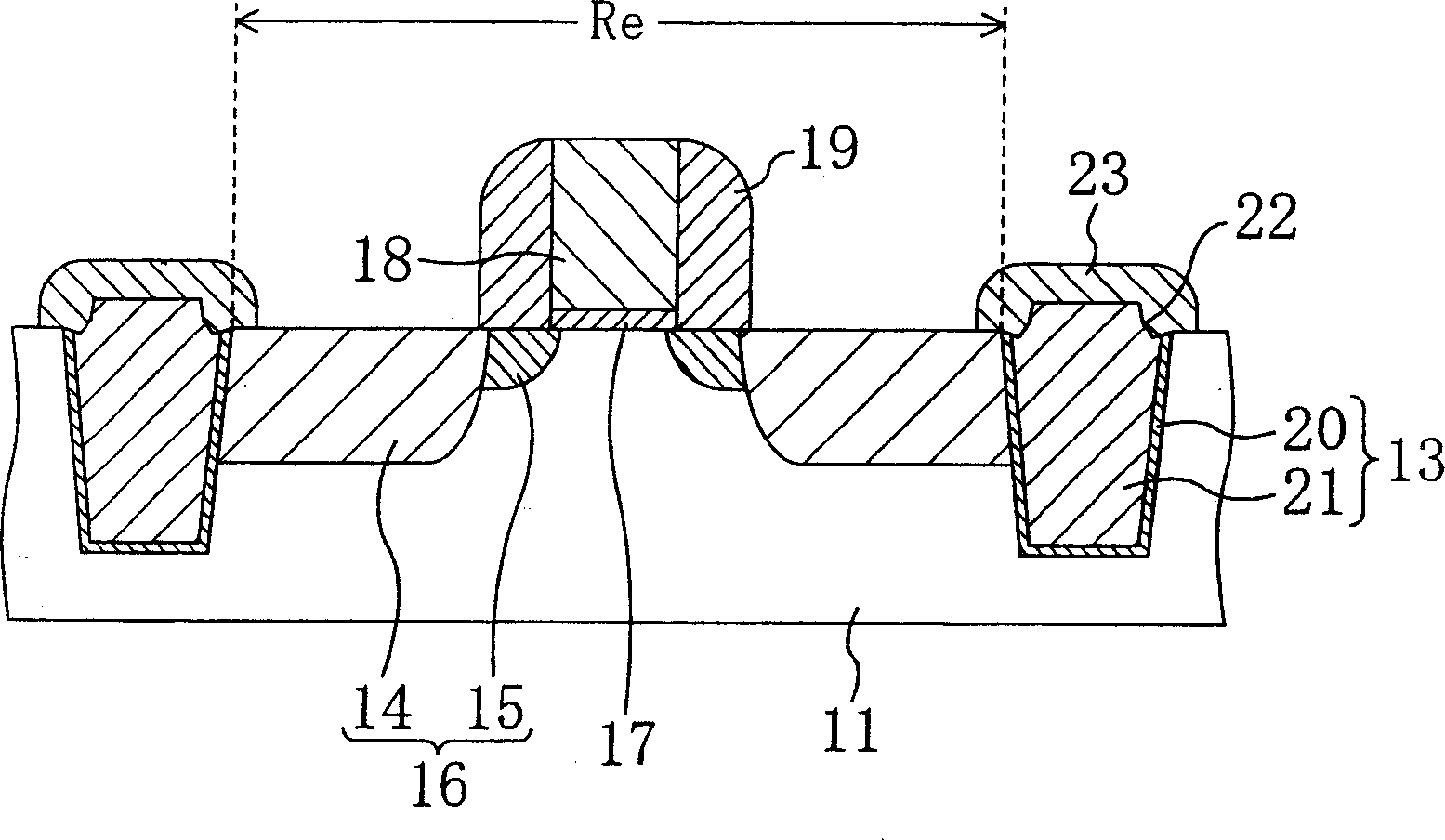

[0044] The semiconductor device of this embodiment is characterized in that the upper surface from the trench element isolation part to the surrounding area of the trench element isolation part located in the element formation region is covered with an oxygen permeation inhibiting film that inhibits supply of oxygen. The following refers to the structure of the semiconductor device of this embodiment figure 1 Be explained. figure 1 It is a cross-sectional view showing the structure of the semiconductor device according to the first embodiment.

[0045] Such as figure 1 As shown, the semiconductor device of this embodiment is constituted by a MISFET provided in the element formation region Re of the semiconductor substrate 11 and a trench element isolation portion 13 surrounding the side surface of the element formation region Re.

[0046] The MISFET is an N-type source-drain region 16 composed of a high-concentration impurity diffusion layer 14 and a low-concentration i...

Embodiment 2

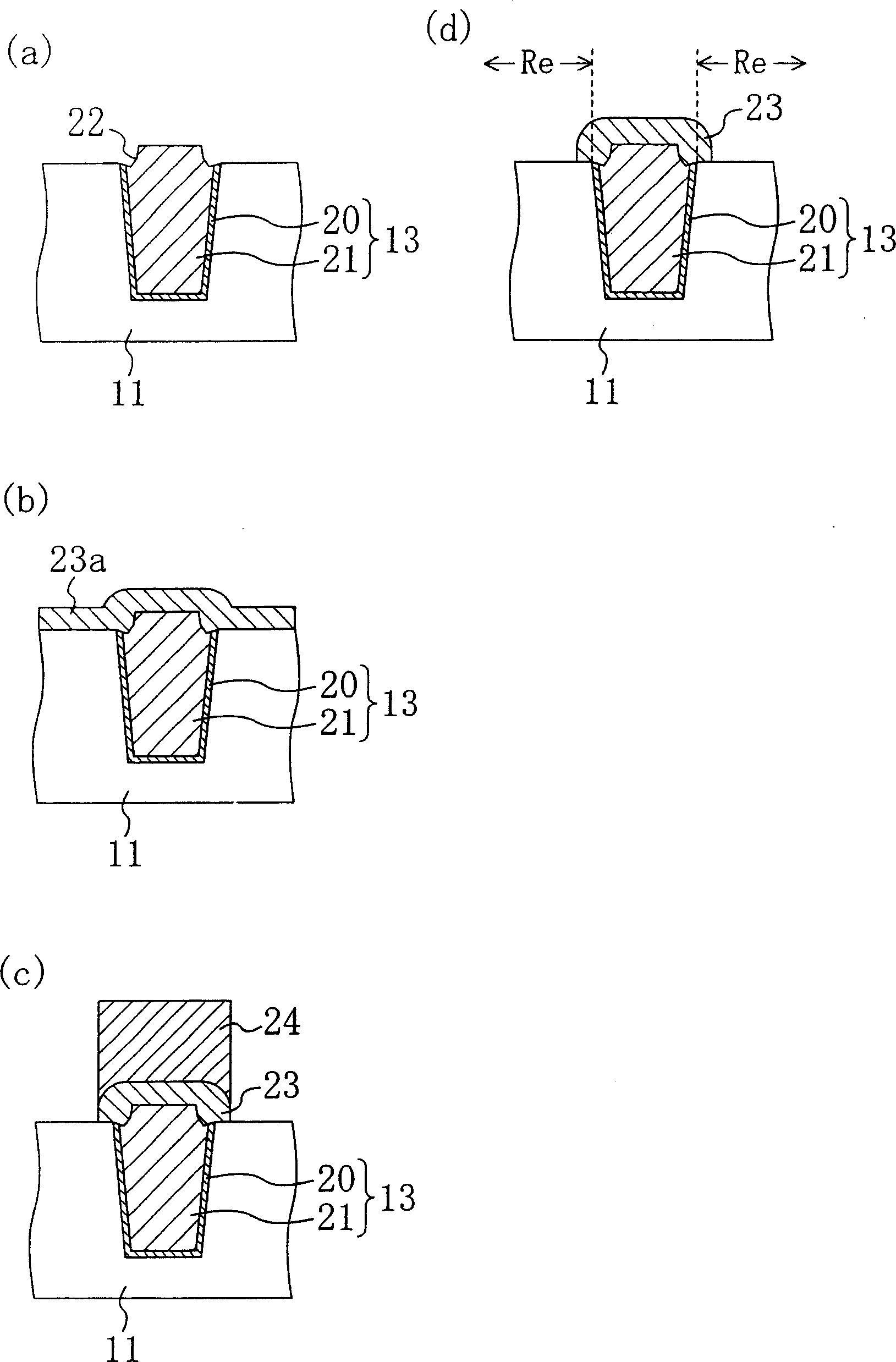

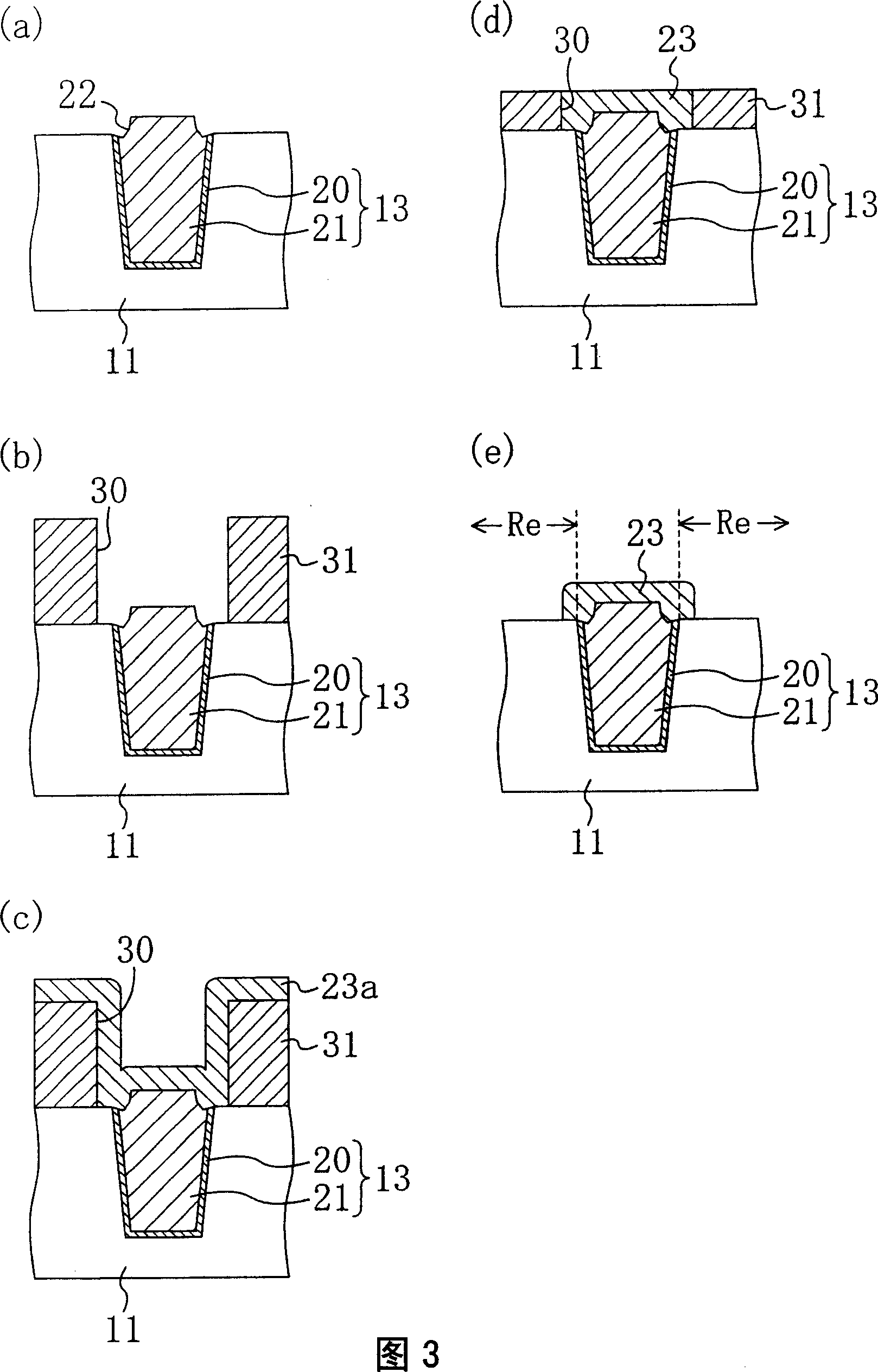

[0067] In this embodiment, a case where the oxygen gas permeation suppressing film is used to cover not the entire upper part of the trench device isolation part but only the boundary part between the trench device isolation part and the device isolation part forming region will be described.

[0068] Figure 4 It is a cross-sectional view showing the structure of the semiconductor device of the second embodiment.

[0069] Such as Figure 4 As shown, in the semiconductor device of this embodiment, the step portion 22 is formed on the outer edge portion of the trench device isolation portion 13 . Usually, the level difference portion 22 is naturally formed when the protective oxide film covering the element formation region Re of the semiconductor substrate 11 is removed during the formation process of the trench element isolation portion 13 . However, the step portion 22 may be gradually formed during other steps, or may be formed intentionally. The oxygen gas passage suppr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com