Device for controlling interior storage of chip and its storage method

An on-chip storage and control chip technology, applied in the field of computer communication, can solve problems such as large performance differences, inability to change, and difficulty

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

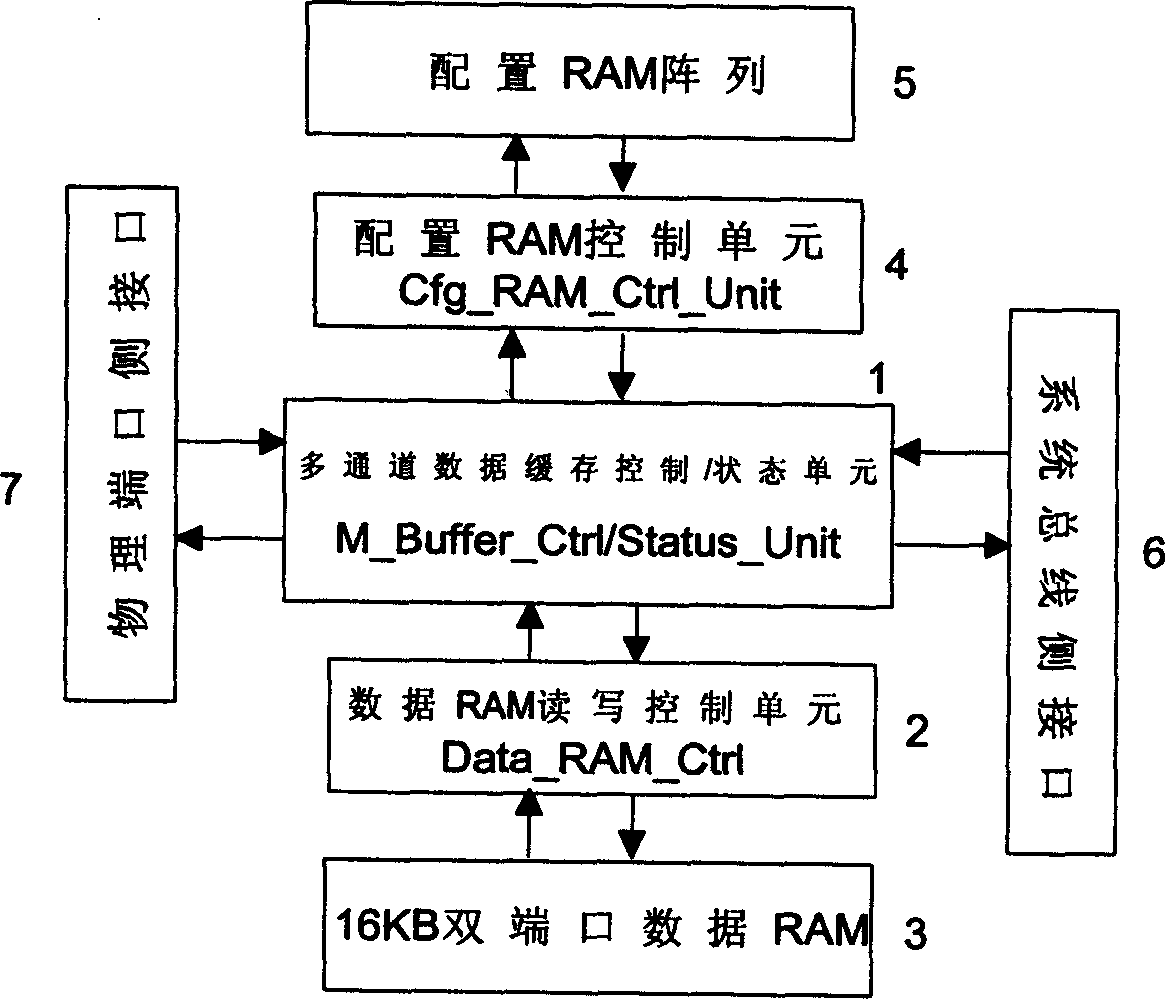

[0079] The control chip on-chip storage device of the present invention is shown in Figure 2, and its structure comprises:

[0080] Multi-channel data cache control / status unit (i.e. M_Buffer_Ctrl / Status_Unit) 1: provides the data interface between the control chip and each channel, including the physical port side interface 7 and the system bus side interface 6; and is used to coordinate the data RAM read and write control unit and Configure the synchronous operation between the RAM control units, maintain the channel storage state information, that is, maintain the channel linked list status information of each channel; the channel linked list refers to a linked list structure storage area allocated for the channel in the dual-port data storage RAM, The status information of the channel linked list is used to indicate the occupation of the storage area by the channel data;

[0081] The channel linked list state information includes:

[0082] The signal "Exist.EOF" of the ch...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com