Phase-locked loop frequency synthesizer with digital coarse tuning loop

A frequency synthesizer and coarse tuning technology, applied in the direction of automatic power control, electrical components, etc., can solve the problems of increasing the cost of frequency synthesis, low integration, and no degradation of frequency synthesis performance, and achieves a reduction in frequency locking time, Improves tuning speed and reduces phase noise

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

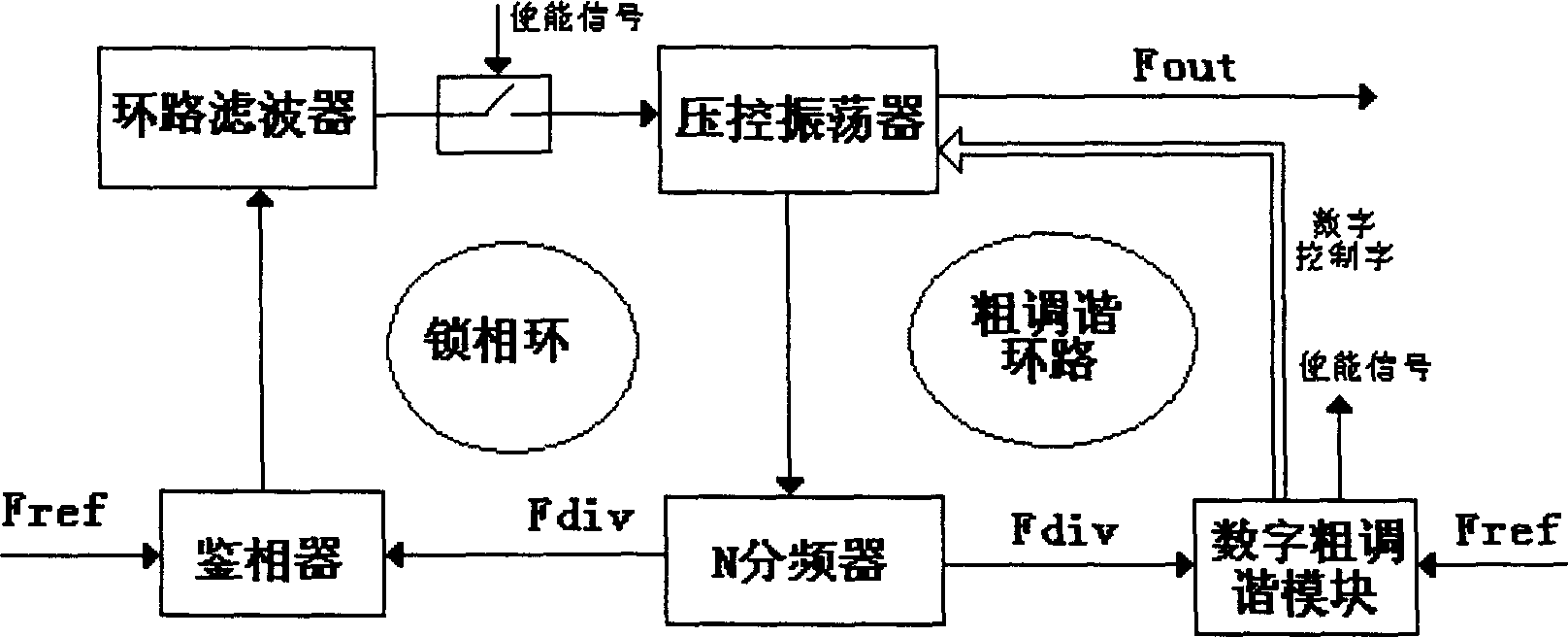

[0021] The structure and operating principle of a kind of PLL frequency synthesizer with high precision digital coarse tuning loop that the present invention proposes are described in detail as follows in conjunction with accompanying drawing and embodiment:

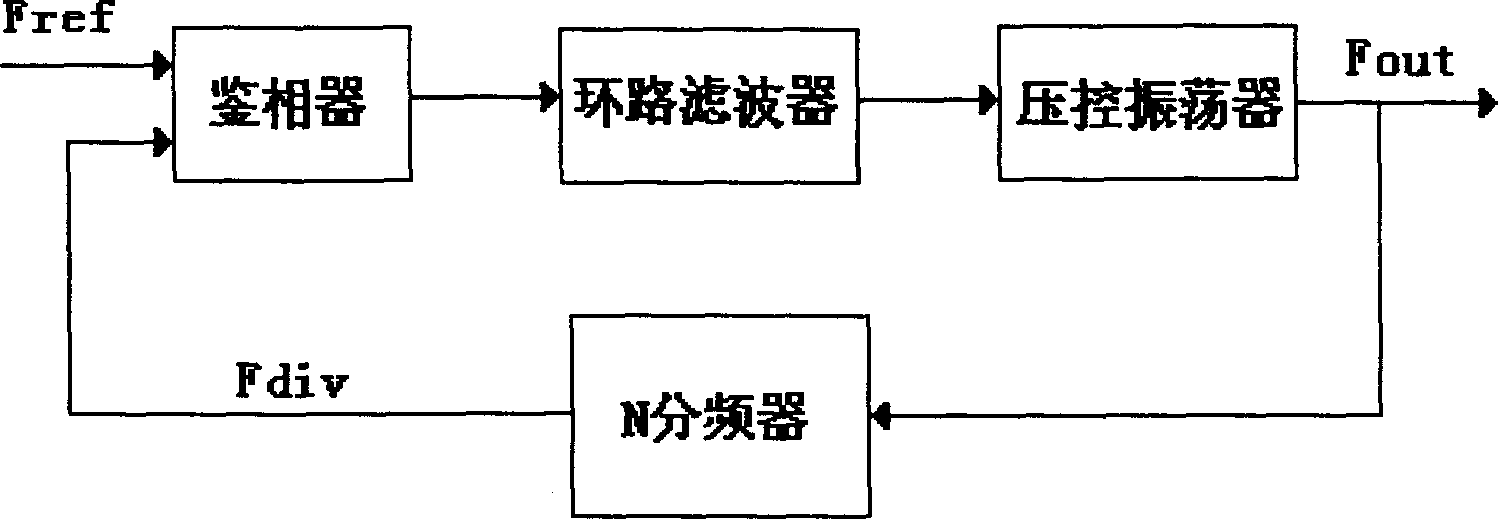

[0022] The overall structure of frequency synthesis of the present invention is as image 3 As shown, it includes two tuning loops, in which the phase-locked loop is still composed of a phase detector, a loop filter, a voltage-controlled oscillator and an N frequency divider. The connection relationship and working principle are the same as those of the traditional PLL frequency Comprehensively the same; the increased coarse tuning loop consists of a voltage-controlled oscillator, an N frequency divider, and a digital coarse tuning module connected to the output of the voltage-controlled oscillator and the input of the N frequency divider. In this frequency synthesis structure, the voltage-controlled oscillator and the N...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com