Non-volatile memory with float gate wall and its preparing process

A non-volatile, manufacturing method technology, used in semiconductor/solid-state device manufacturing, electrical solid-state devices, semiconductor devices, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

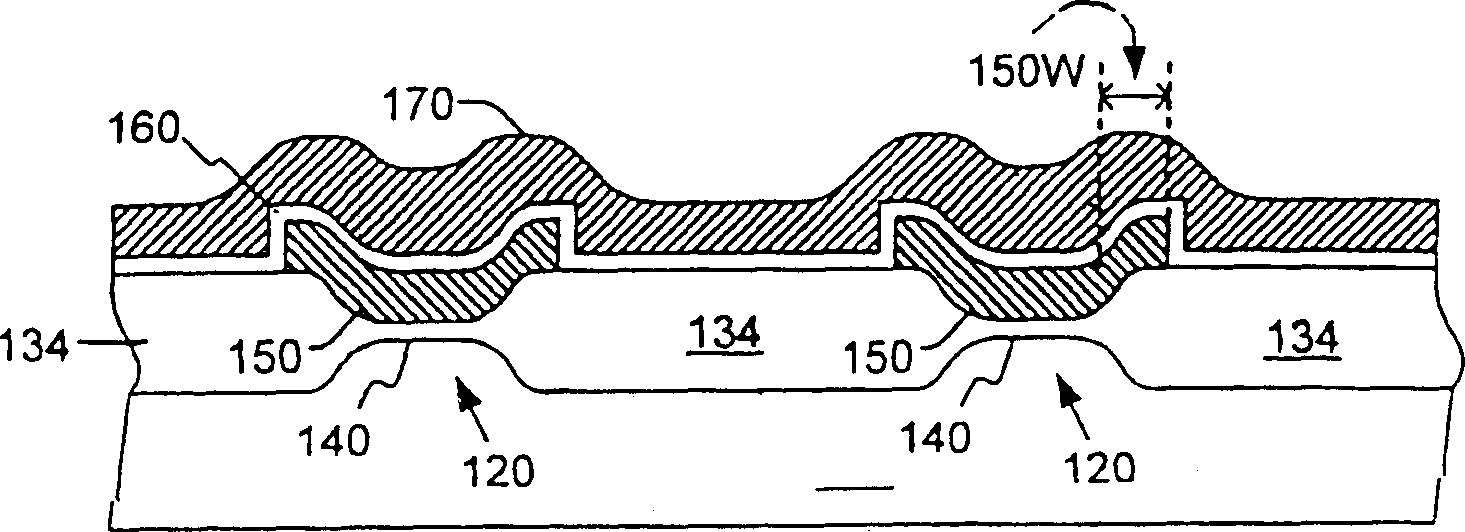

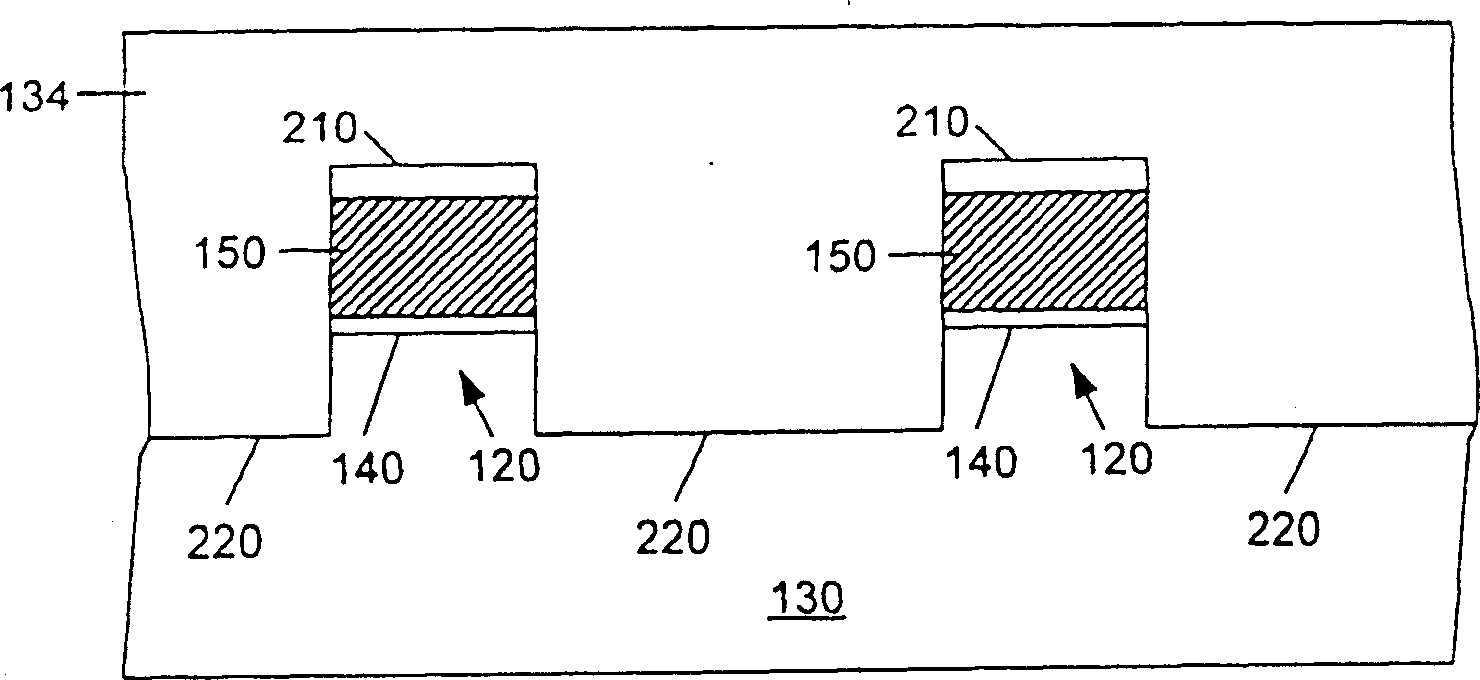

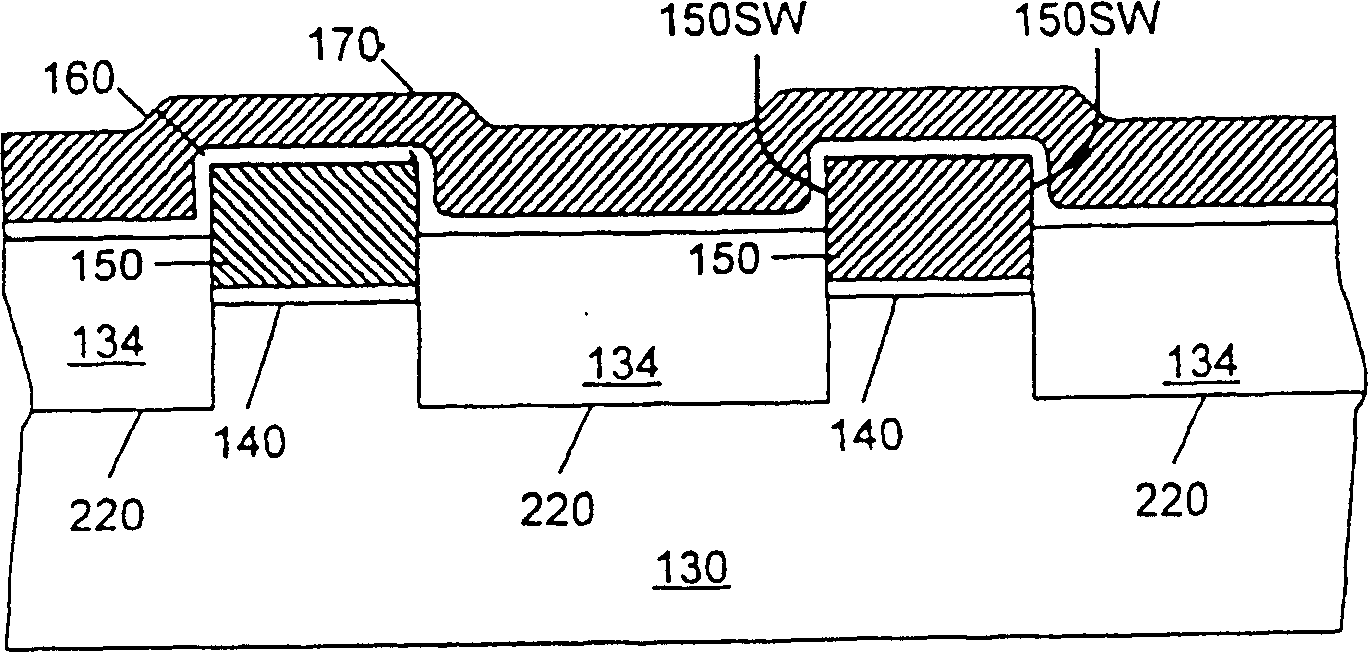

[0015] Figure 4 It is a cross-sectional view of a non-volatile memory structure generated in the pre-manufacturing stage. A floating gate polysilicon layer 150 self-aligned with the active region 120 is formed by known shallow trench isolation (shallow trench isolation, STI) technology, basically the same as figure 2 Similarly, in this embodiment, the substrate 130 is a suitably doped (such as doped with phosphorus) single crystal silicon substrate, and a suitable well (well) (not shown) can be formed in the substrate 130, as H.T.Tuan et al. Patent application No. 09 / 640,139 titled "Nonvolatile Memory Structures and Methods of Fabrication" (application date August 15, 2000) described in the patent, of course other types of substrates can also be used here, such as non-silicon substrates, the present The invention is not limited to a particular kind of well or doping pattern.

[0016] An insulating layer 140 is formed on the substrate 130. In this embodiment, the insulating ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com