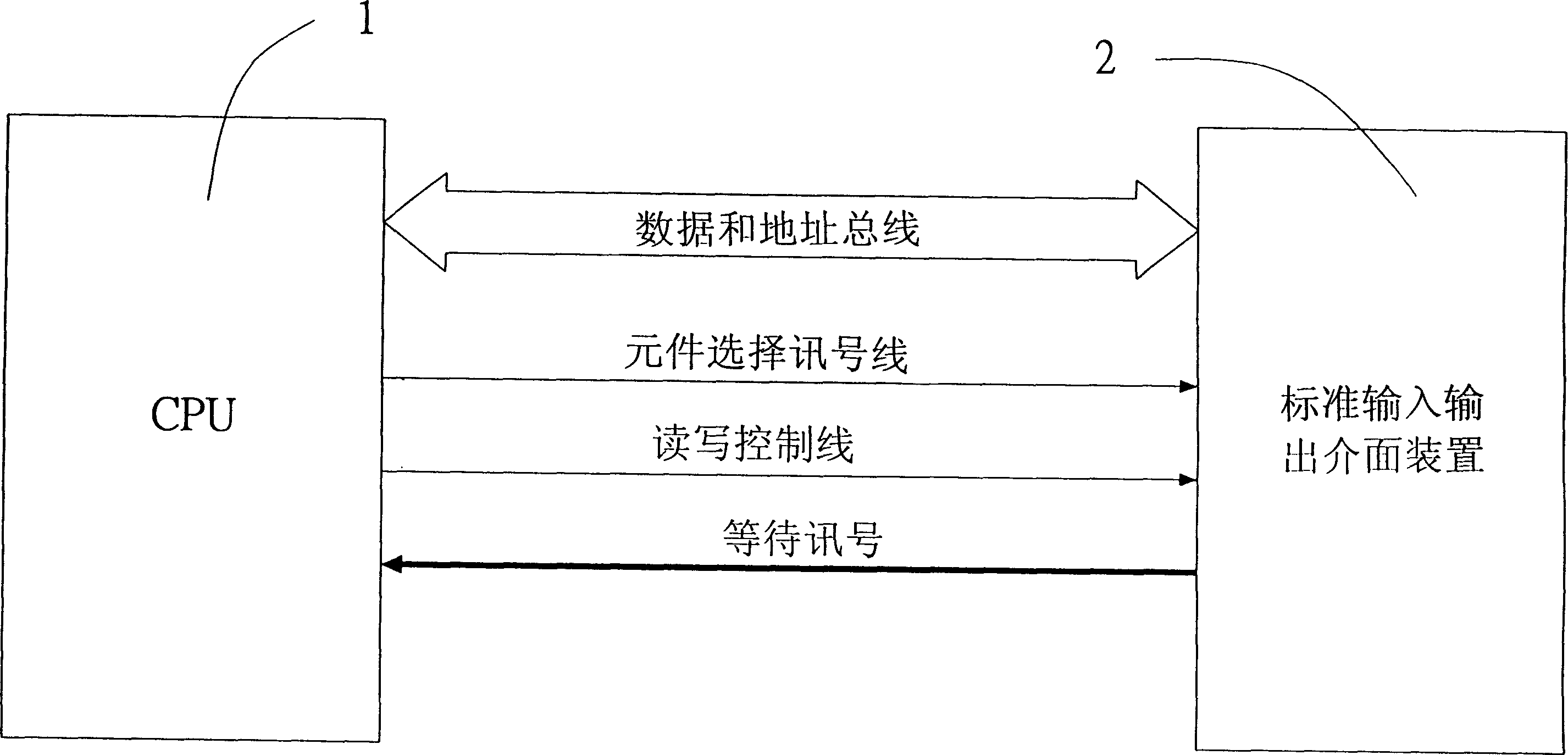

Circuit for harmonizing read and wright between central processor and input output interface device

A central processing unit, input and output technology, applied in electrical digital data processing, instruments, etc., can solve problems such as slow speed, data transmission errors, and inability to confirm in time, so as to reduce system design problems and avoid transmission errors.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] see Image 6 Shown, the present invention is to set up a synchronous control unit 3 and a signal input unit 5 between CPU (central processing unit) 1 and PCMCIA Card (standard input and output interface device) 2 with reference to shown in Fig. 7,8, wherein this synchronous control Unit 3 may include:

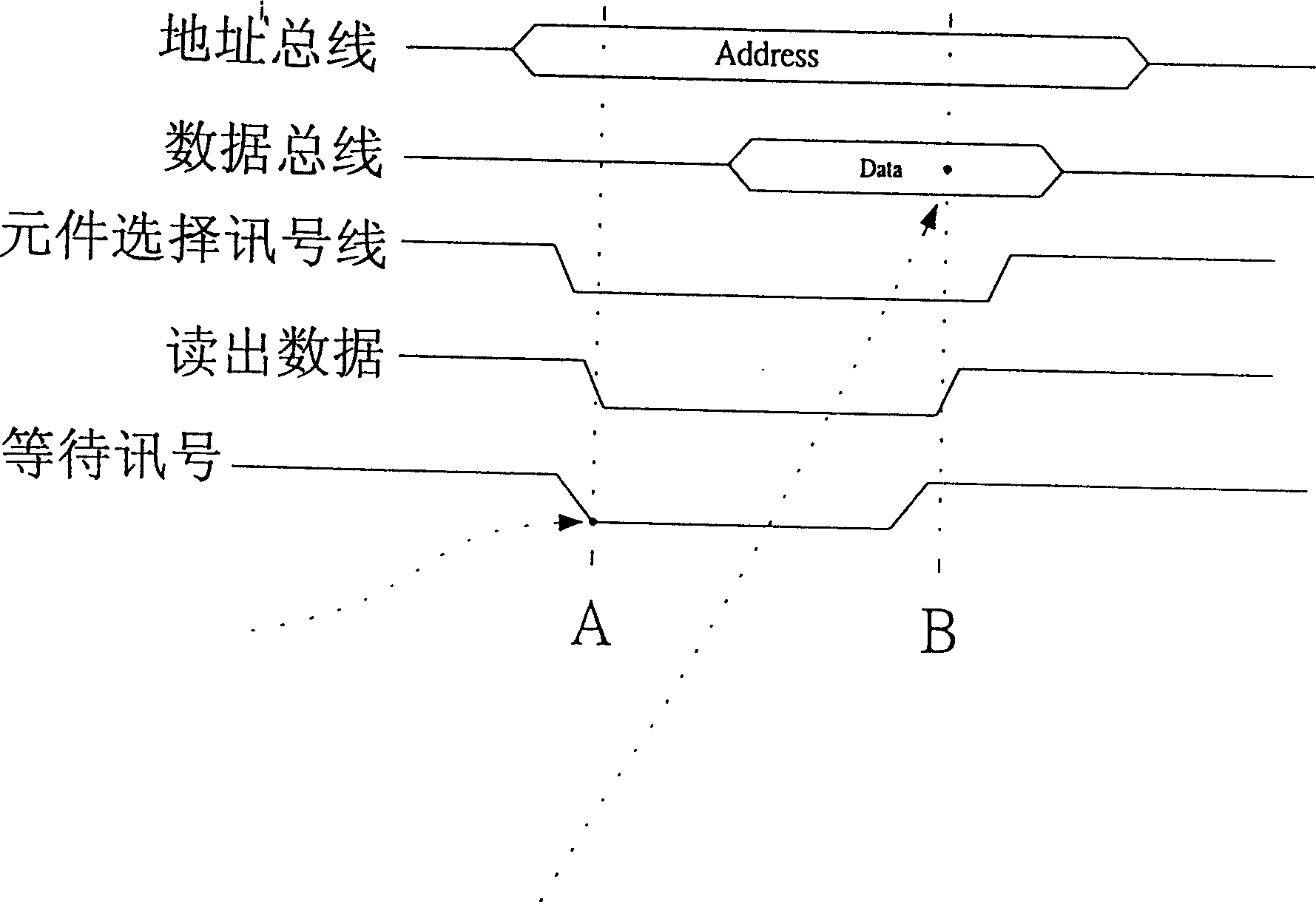

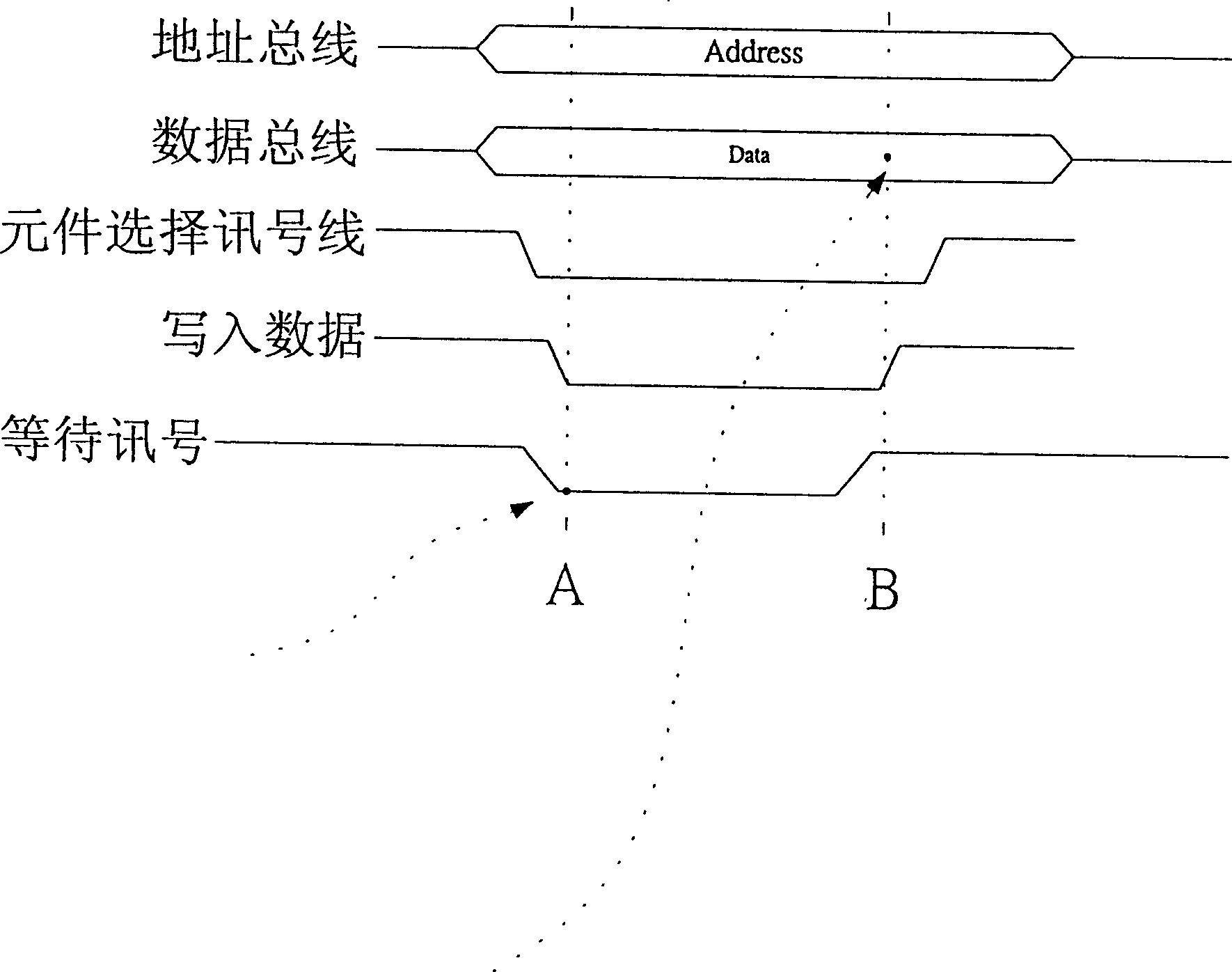

[0033] An inverter 31, the input terminal is connected to the output terminal of a read-write signal extractor 32, and the reverse output terminal is connected to one input terminal of the first comparison logic gate 33, and is controlled by the trigger terminal When the connected CPU (Central Processing Unit) 1 is input with timing pulse (Clock) 4, the reverse output terminal can provide a reverse sync pulse status.

[0034] A read-write signal picker 32, the input end is respectively connected with the signal control lines of the read end (READ) and the write end (WRITE), and the output end is connected to the input end of an inverter 31, when When one of the read te...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com