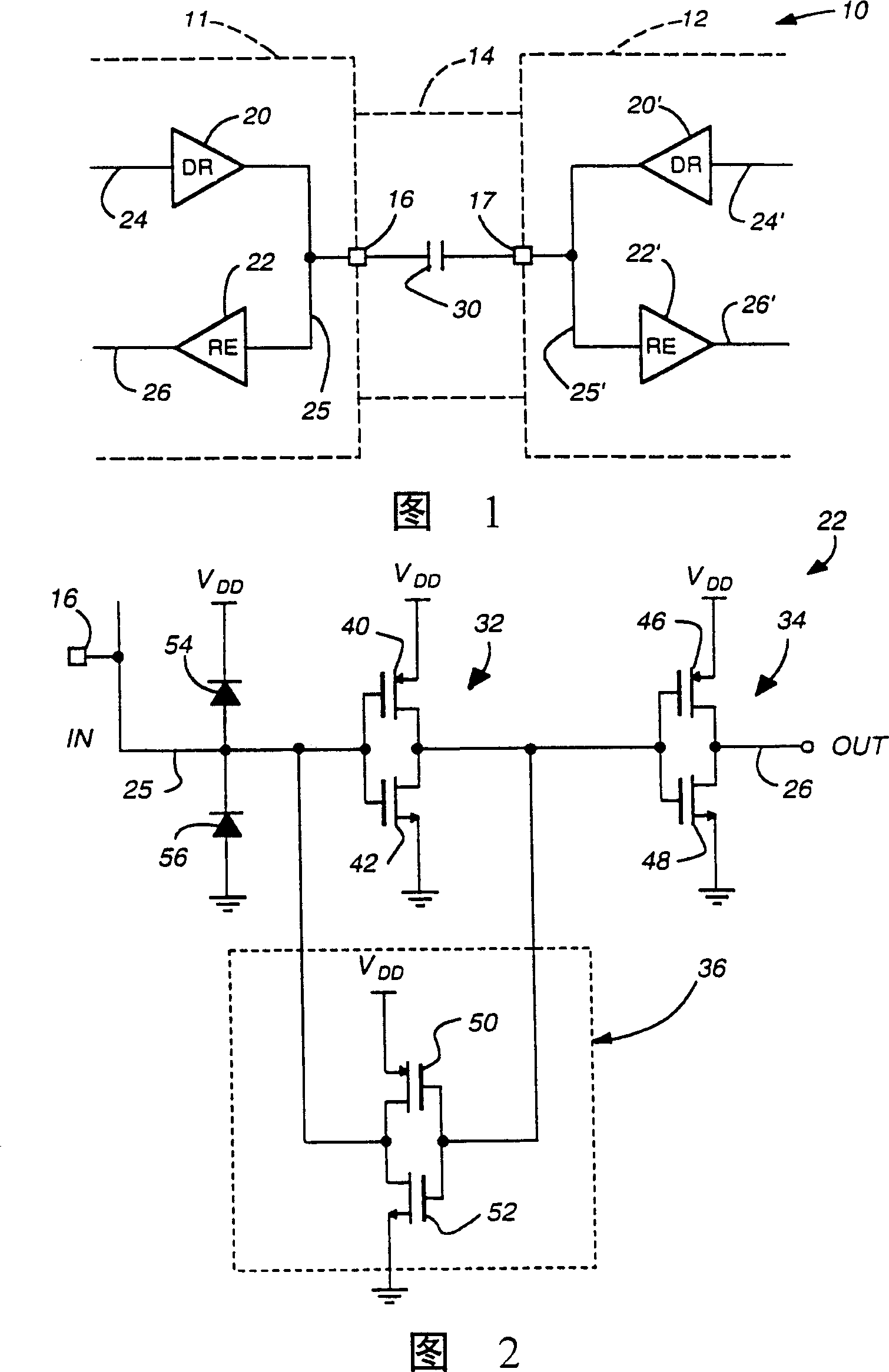

Method and apparatus for galvanically isolating two integrated circuits from each others

An integrated circuit, DC isolation technology, applied in the direction of circuit, logic circuit connection/interface layout, logic circuit coupling/interface for bidirectional operation, etc., to achieve the effect of reducing area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] It should be noted that the process steps and structures described here are not necessary to form a complete process flow for fabricating integrated circuits. It is contemplated that the present invention may be practiced in conjunction with integrated circuit fabrication techniques currently used in the art, and only the inclusion of such conventional process steps is necessary for an understanding of the present invention.

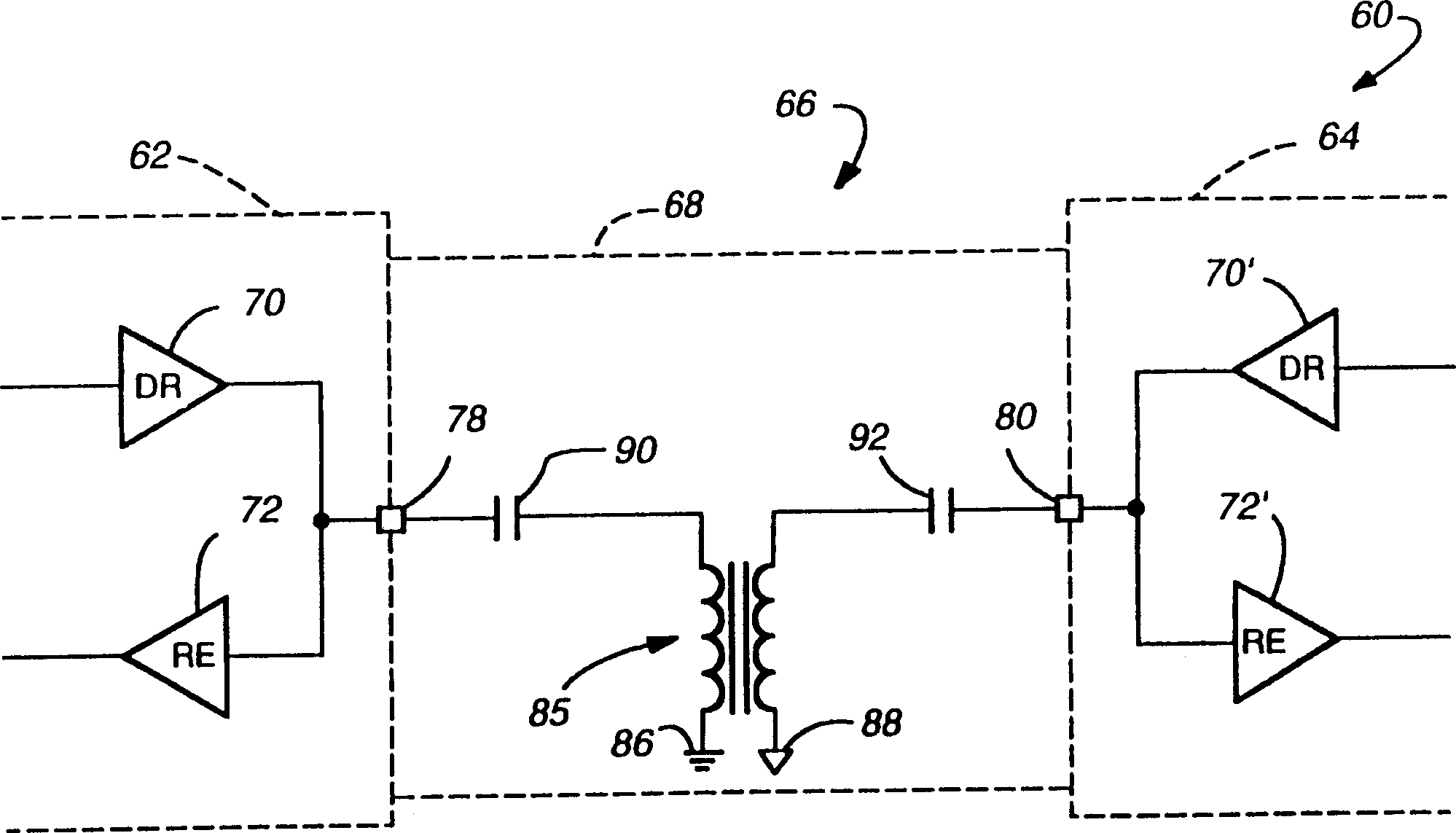

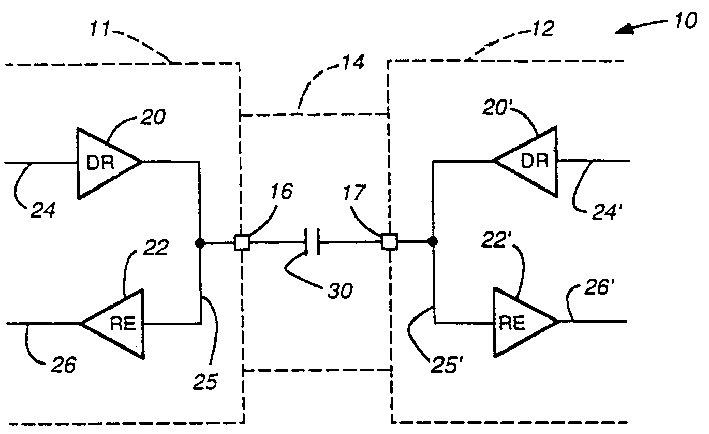

[0034] The improved solution of the present invention is to use a lock input and a standard CMOS output connected by a capacitor, which acts as an isolation barrier. Since the charge on the capacitor cannot change instantaneously, a CMOS output on one side of the isolation barrier raises or lowers the corresponding input on the other side of the isolation barrier. At this point, the latch input holds the charge on the capacitor until the output changes in the other direction.

[0035] It will become apparent that, compared to prior art swings of ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com