Semiconductor structure and forming method thereof

A semiconductor and gate structure technology, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve the problems that the performance of fin field effect transistors needs to be improved, so as to reduce parasitic capacitance and improve performance Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] It should be noted that "surface" and "upper" in this specification are used to describe the relative positional relationship in space, and are not limited to whether they are in direct contact.

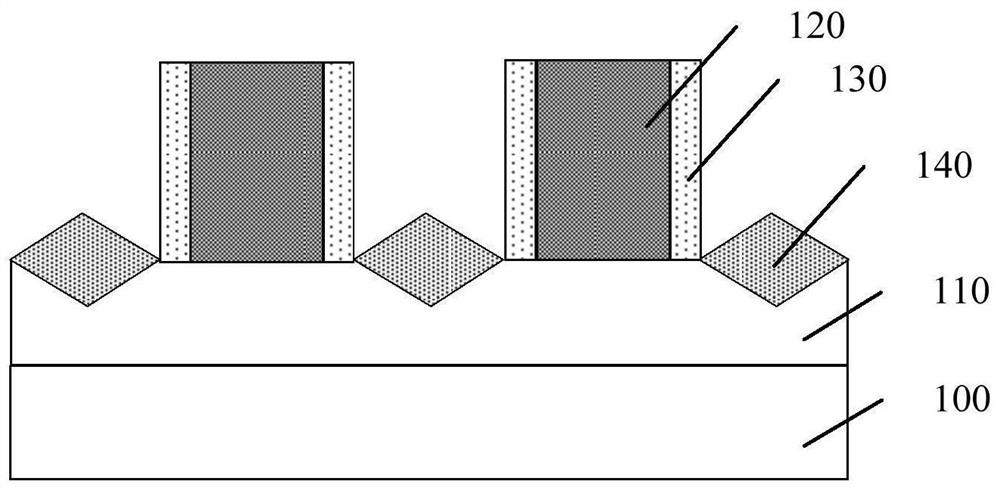

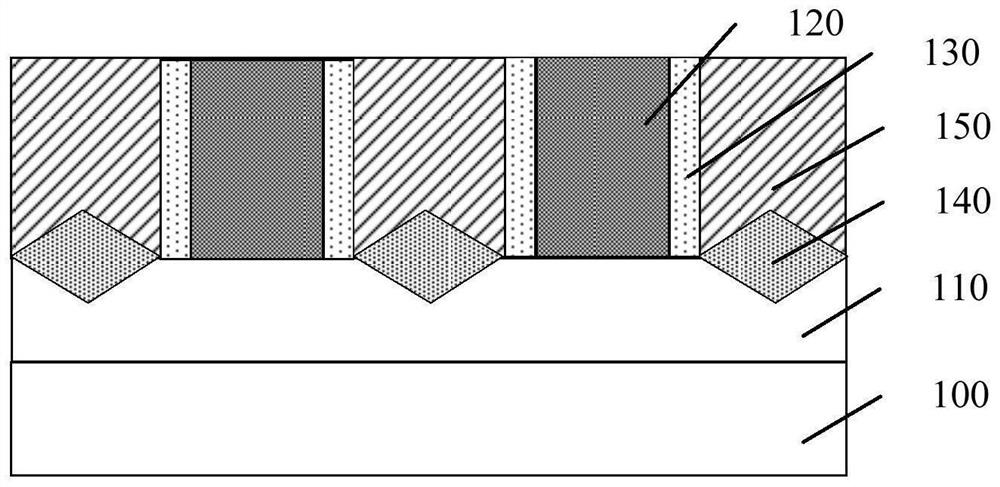

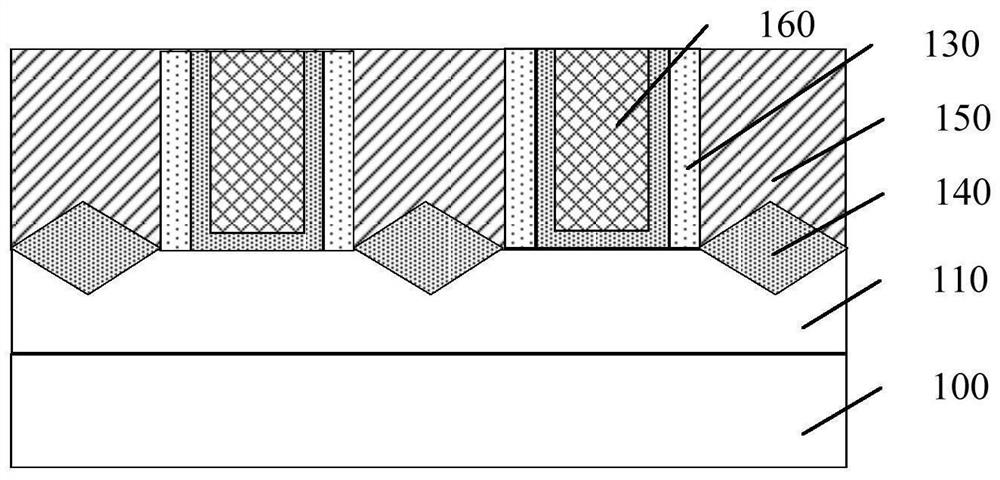

[0043] First, the reasons for the poor performance of the existing semiconductor structure are described in detail with reference to the accompanying drawings. Figure 1 to Figure 4 It is a structural schematic diagram of each step of a method for forming a conventional semiconductor structure.

[0044] Please refer to figure 1 , a substrate 100 is provided, the substrate has a fin 110 and a dummy gate structure 120 , the dummy gate structure 120 spans the fin 110 , and the dummy gate structure 120 is located on the fin 110 Part of the top surface and sidewall surface; forming sidewall spacers 130 on the sidewall surfaces of the dummy gate structure 120 ; forming source and drain doped regions 140 in the fins 110 on both sides of the dummy gate structure 120 and the sidewall ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com