LPDDR wafer RDL design method suitable for multi-chip failure analysis

A technology of failure analysis and design method, applied in semiconductor/solid-state device components, semiconductor/solid-state device testing/measurement, semiconductor devices, etc., can solve problems such as indistinguishable, time-consuming, and difficult processes

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The technical solutions in the embodiments of the present invention will be clearly and completely described below with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only a part of the embodiments of the present invention, rather than all the embodiments.

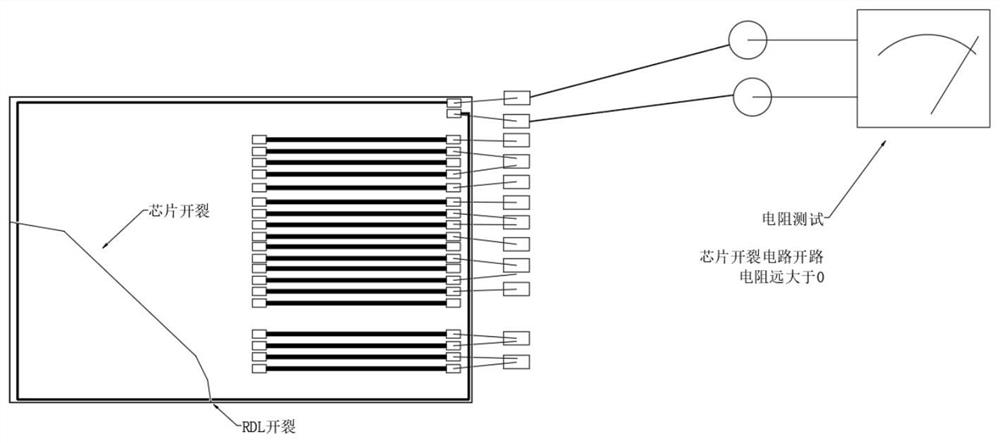

[0030] refer to Figure 1-4 , an LPDDR wafer RDL design method suitable for multi-chip failure analysis, including the following steps:

[0031] S1: Based on the conventional LPDDR RDL design, increase the bonding welding position;

[0032] Specifically, the conventional RDL is designed to guide the die edge from the middle pad to form a new pad.

[0033] S2: Design the packaging substrate and add several gold fingers on the front of the substrate for DIE connection;

[0034] S3: Encapsulate and connect the bonding pads with the gold fingers on the front of the substrate;

[0035] S4: Measure the resistance, judge the DIE state through ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com