Method for converting flash into ROM and semiconductor device thereof

A technology of semiconductor and memory unit, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, electric solid-state devices, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

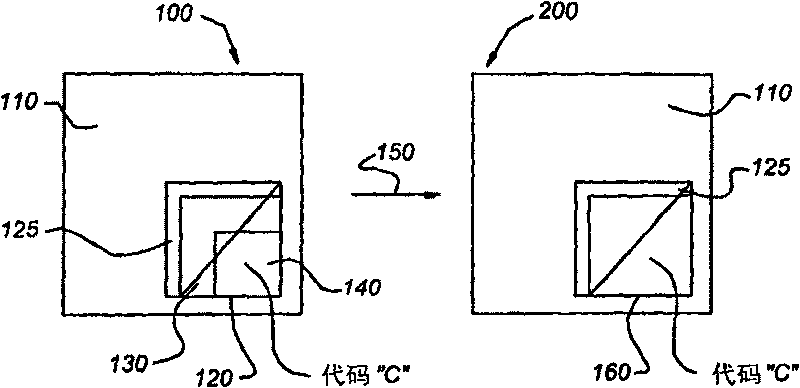

[0054] figure 1 Flash-ROM conversion of an SOC device is schematically shown.

[0055] The first SOC device 100 includes a device portion 110 produced by a baseline technology. Embedded in device portion 110 is Flash portion 120 . Symbolically, the wiring scheme between device portion 110 and Flash portion 120 is represented by region 125 . The flash memory part 120 includes a peripheral circuit 130 and a flash memory part 140 . The peripheral circuit 130 is connected to the wiring scheme 125 of the device portion 110 at one end, and is connected to the flash memory portion 140 at the other end. The flash memory portion 140 includes a plurality of flash memory cells, and the flash memory portion 140 is configured to store the program code C in the plurality of flash memory cells. Program code C relates to a program that provides functionality to the SOC device 100 during operation of the SOC device 100 .

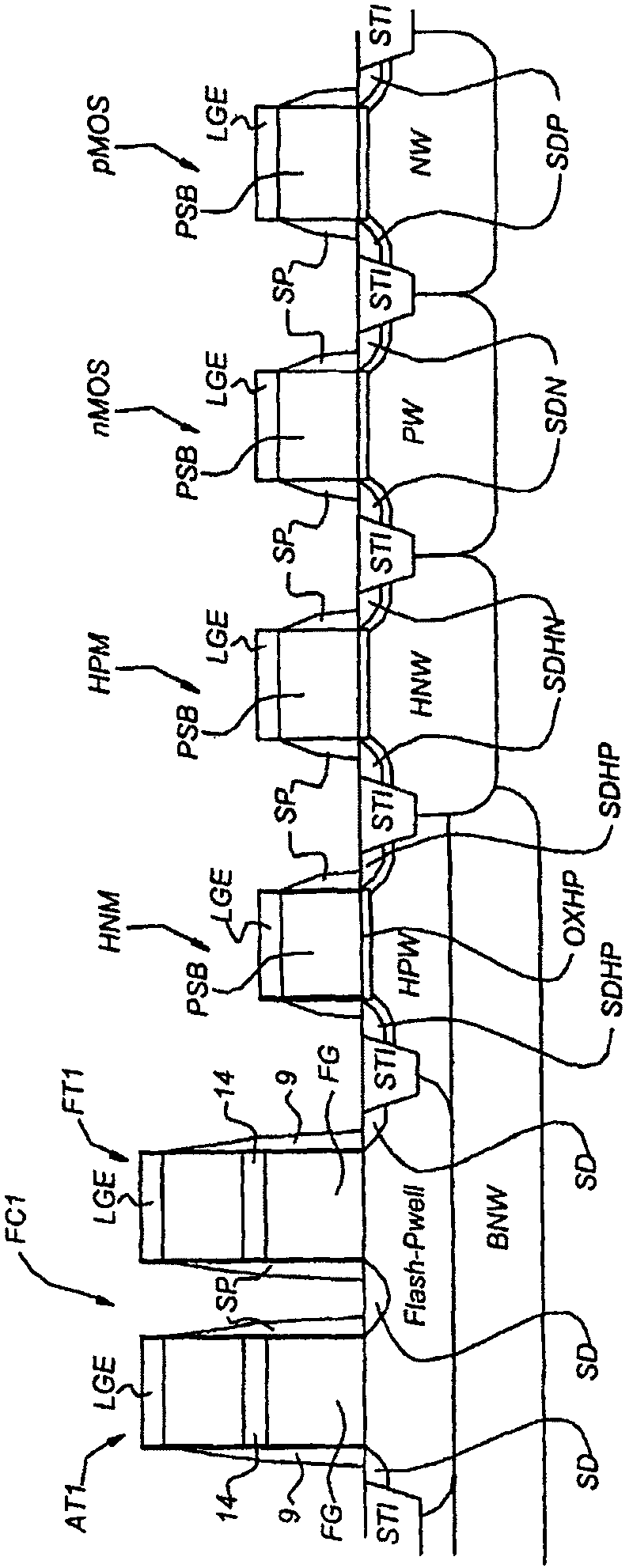

[0056] Peripheral circuitry 130 includes high voltage driver circu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com