Field programmable gate array (FPGA) interconnection resource test algorithm based on graph reinforcement learning

A technology of interconnected resources and reinforcement learning, applied in the field of FPGA testing, can solve problems such as long test time, lack of versatility, and inability to meet chip test requirements, and achieve low test cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] In order to make the object, technical scheme and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with accompanying drawing:

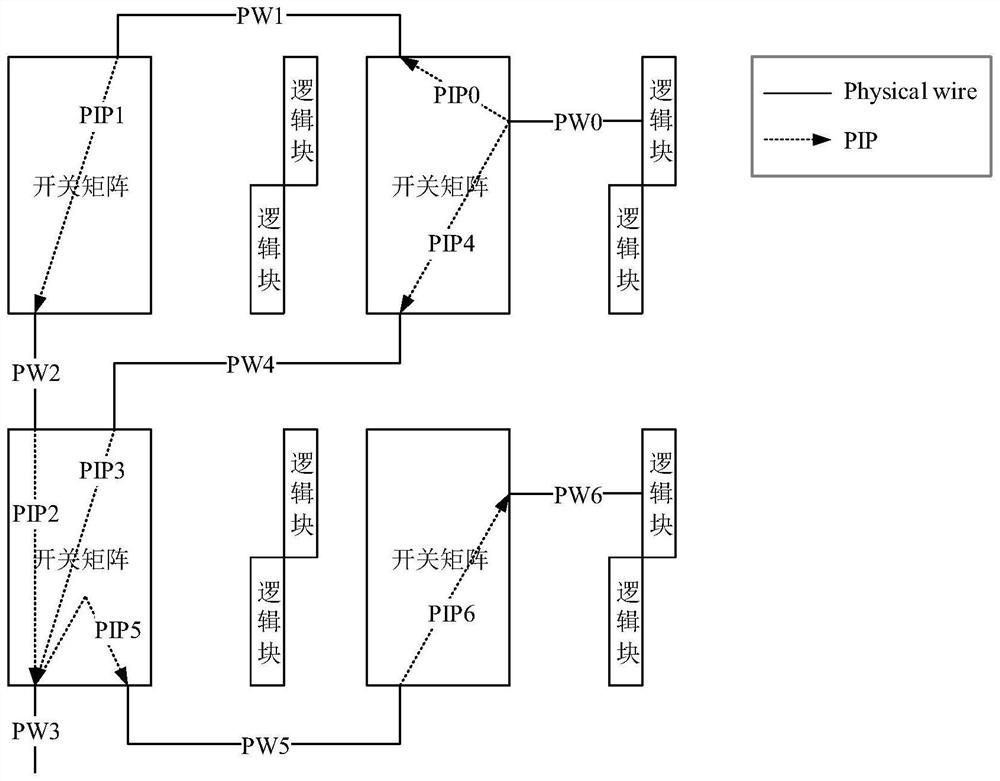

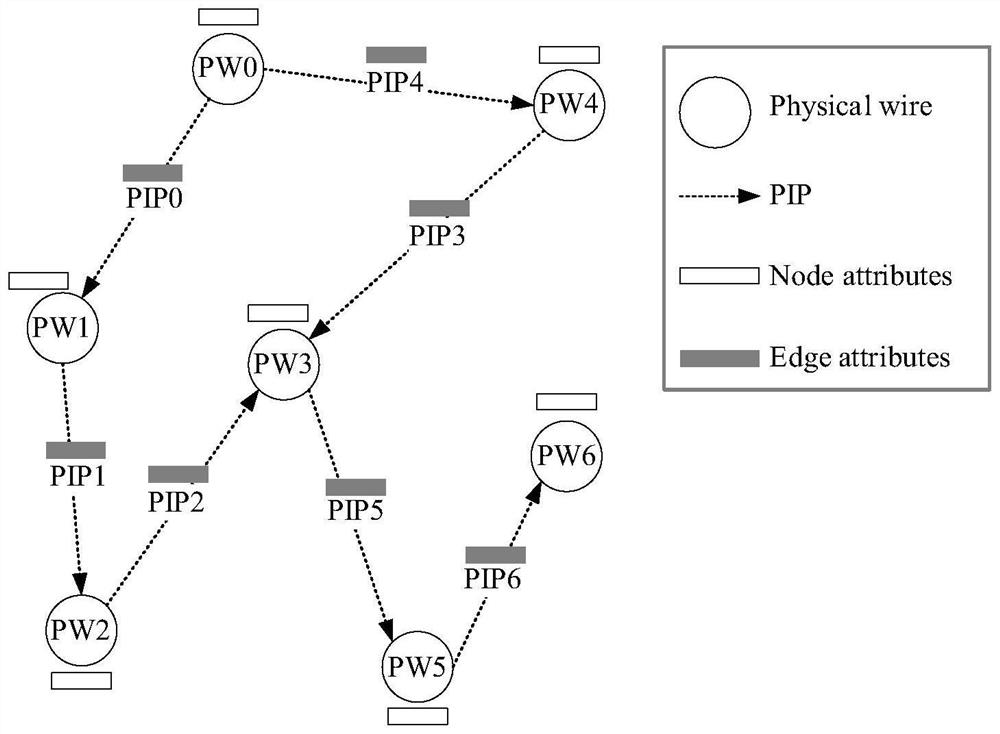

[0028] 1) Abstract interconnected resources into an interconnected resource graph. For an example of the connection relationship of FPGA internal interconnection resources, see figure 1 , abstract the connection relationship of FPGA interconnect resources into a mathematical concept graph (Graph), which is called interconnect resource graph, such as figure 2 , a node (node) represents a physical wire (Physical wire) in the FPGA interconnection resource, and an edge (edge) represents a programmable interconnection point (Programmable Interconnection Point, hereinafter referred to as PIP) in the FPGA interconnection resource. At the same time, each node has node attributes (Node attributes), and each edge has edge attributes (Edge attributes). These attribute information...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com