Wafer-level packaging sensibilization and noise reduction structure of miniature electric field sensor

An electric field sensor, wafer-level packaging technology, applied in microelectronic microstructure devices, microstructure technology, microstructure devices and other directions, can solve problems such as complex process flow, improve noise reduction performance, increase output induced current, Simple and effective manufacturing process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0050] The manufacturing process steps of a miniature electric field sensor wafer-level package sensitivity-increasing and noise-reducing structure of the present disclosure are as follows.

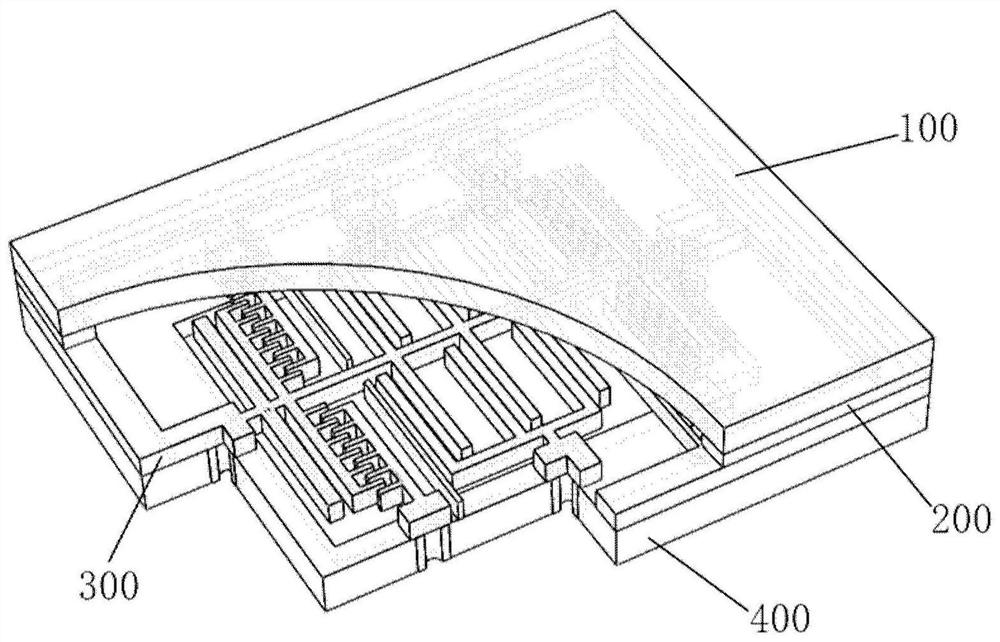

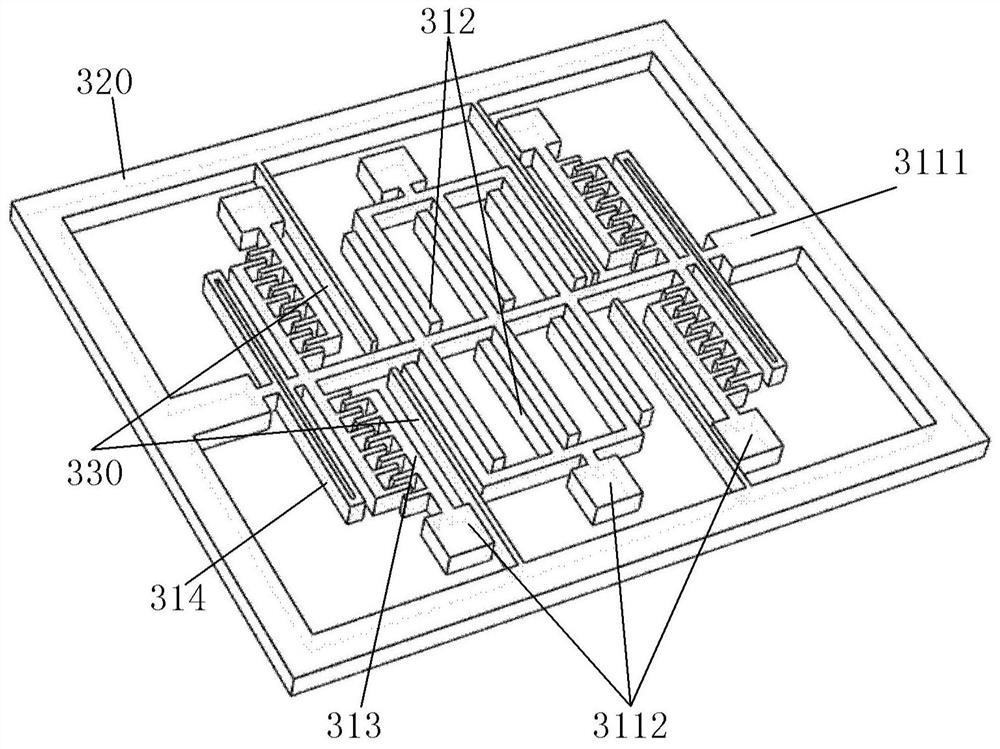

[0051] refer to Figure 4 , using the supporting layer of the SOI wafer as the capping layer 100, the structural silicon layer and the buried oxide layer of the SOI wafer are sequentially processed into the device layer 300 and the second insulating layer 200, including: the structure of an SOI wafer The first anchor point 3111, the second anchor point 3112, the sensing structure 312, the driving structure 313, the elastic beam 314, the rectangular closed sealing ring 320 and the shielding beam 330 are etched on the silicon layer to obtain the device layer 300; the release and rectangular sealing ring In the rectangular area corresponding to the inner circle of 320, and removing the buried oxide layer except the positions corresponding to the first anchor point 3111 and the second anchor ...

Embodiment 2

[0055] The preparation steps of another miniature electric field sensor wafer-level packaging sensitivity-increasing and noise-reducing structure of the present disclosure are as follows.

[0056] In this embodiment, the methods for preparing the device layer 300 , the second insulating layer 200 , and the capping layer 100 are the same as those in the first embodiment.

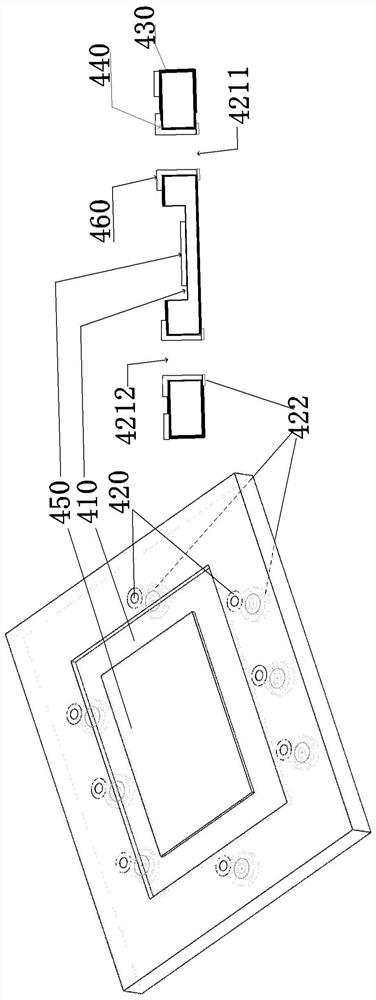

[0057] refer to Figure 7 , etch a groove 410 on a conductive silicon wafer to obtain a base layer 400; grow a first insulating layer 430 on the upper surface of the base layer 400; The window 440 is etched at the position corresponding to the point 3112; the bonding dielectric layer 460 is grown on the position corresponding to the rectangular closed sealing ring 320, the first anchor point 3111, and the second anchor point 3112 of the device layer 300 on the first insulating layer 430, Wherein, the bonding medium layer 460 covers the window 440 on the first insulating layer 430 ; a thin layer of getter 450 i...

Embodiment 3

[0060] On the basis of the second embodiment, this embodiment provides another method for fabricating the vertical interconnection structure 420 .

[0061] In this embodiment, as in Embodiment 2, refer to Figure 4 The method shown prepares the device layer 300, the second insulating layer 200, and the capping layer 100; as in the second embodiment, refer to Figure 7 The method shown prepares the base layer 400 , the first insulating layer 430 , the bonding medium layer 460 , and the thin layer of the getter 450 , and the like.

[0062] refer to Figure 9 First, as in Example 2, in a vacuum environment, the rectangular closed sealing ring 320, the first anchor point 3111, and the second anchor point 3112 prepared on the SOI wafer are bonded to the prepared conductor silicon wafer, At the same time, the activation of the getter 450 is completed; then, silicon is etched at the corresponding positions of the first anchor point 3111 and the second anchor point 3112 at the botto...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com