EDA circuit failure analysis method based on deep metric learning

A technology of metric learning and circuit failure, applied in neural learning methods, electrical digital data processing, biological neural network models, etc., can solve the problems of low simulation efficiency and accuracy, and achieve the effect of excellent simulation speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

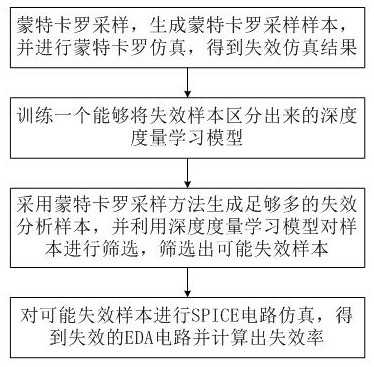

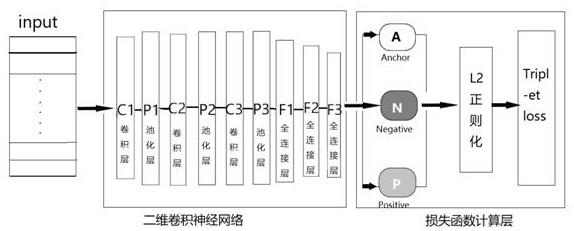

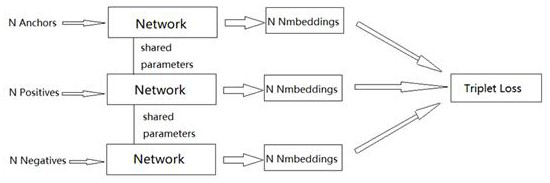

[0028] Such as Figure 1 ~ Figure 4 Shown, the EDA circuit failure analysis method based on deep metric learning of the present invention comprises the following steps:

[0029] Step 1. Perform Monte Carlo sampling on the EDA circuit samples according to the original distribution, generate Monte Carlo sampling samples, and perform Monte Carlo simulation to obtain failure simulation results;

[0030] In specific implementation, the Monte Carlo (MC) method generates a large number of samples through random sampling, according to the formula unit failure rate p cell for Among them, I cell It is an indicator function for judging whether a circuit fails or not, and X is an N-dimensional random vector [x 1 , x 2 , x 3 ......x N ] T , x i (i=1, 2,..., N) is a sampling sample that satisfies the process deviation distribution, f(x) is a function to measure circuit performance, f 0 is the critical value, N is the total number of samples, and the value of i is a natural numbe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com