Array substrate, display panel and display device

A technology for array substrates and substrate substrates, applied in nonlinear optics, instruments, optics, etc., can solve problems such as limited aperture ratio, achieve the effects of reducing line width, improving display effect, and increasing light transmission area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

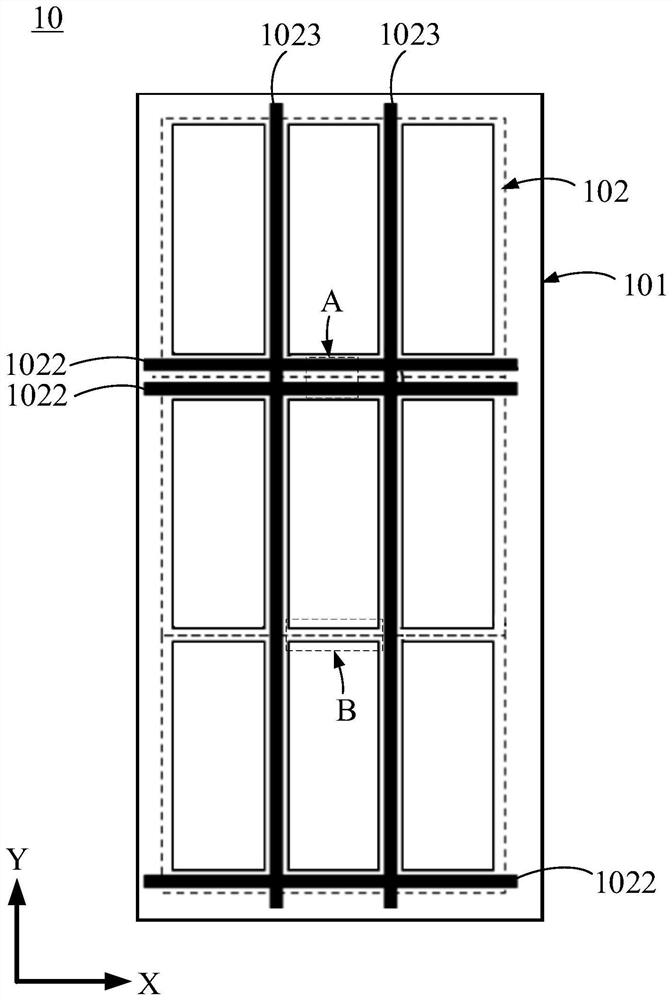

[0044] like figure 1 As shown, an embodiment of the present disclosure provides an array substrate 10 , and the array substrate 10 may include a base substrate 101 and a plurality of sub-pixels 102 .

[0045] The base substrate 101 may be a glass substrate, but not limited thereto, and may also be a substrate made of other materials, such as PI material and the like.

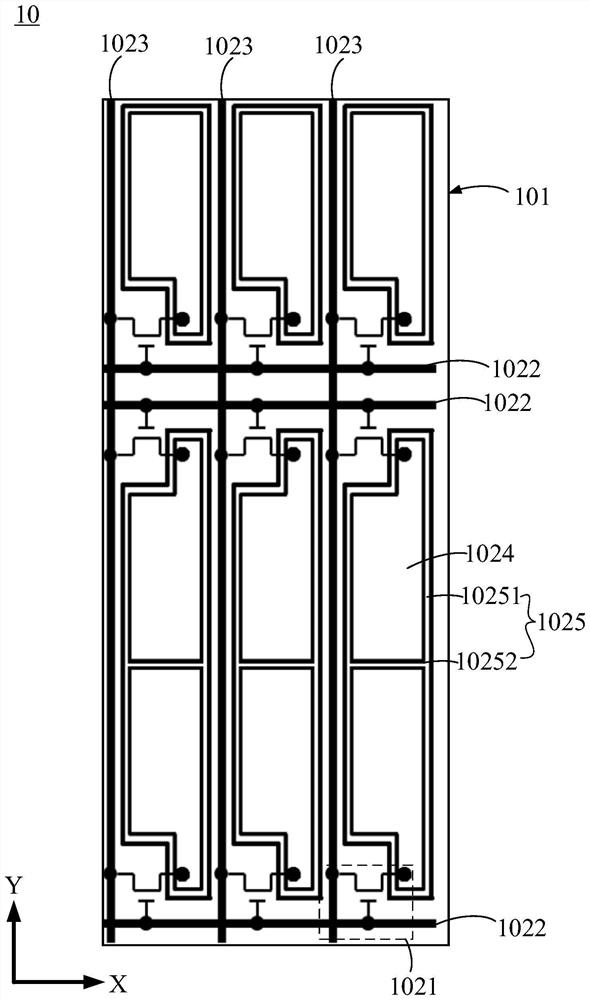

[0046] combine figure 1 and figure 2 As shown, a plurality of sub-pixels 102 may be arrayed on the base substrate 101 along the row direction X and the column direction Y, and the sub-pixels 102 may include transistors 1021 , pixel electrodes 1024 , common electrodes 1025 , data lines 1023 and scan lines 1022 .

[0047] Specifically, the transistor 1021 may include a gate electrode not shown in the figure, an active layer, and a first electrode and a second electrode disposed in the same layer, and a gate insulating layer may be provided between the gate electrode and the active layer, so that the gate The ...

Embodiment 2

[0077] The main difference between the second embodiment and the first embodiment is: image 3 As shown, the arrangement of any two adjacent rows of sub-pixels 102 in the second embodiment is centrally symmetric. For other designs, reference may be made to the content of the first embodiment, which will not be repeated here.

[0078] It should be noted that the second embodiment mentioned that the arrangement of any two adjacent rows of sub-pixels 102 is arranged symmetrically in the center, in order to indicate that the arrangement of the sub-pixels 102 adopts a flip (flip) design, that is, as follows: image 3 As shown, the transistors 1021 of the sub-pixels 102 in the odd-numbered rows are connected to the data lines 1023 on the left, and the transistors 1021 of the sub-pixels 102 in the even-numbered rows are connected to the data lines 1023 on the right. Design space for the transistor 1021 of the pixel 102 .

Embodiment 3

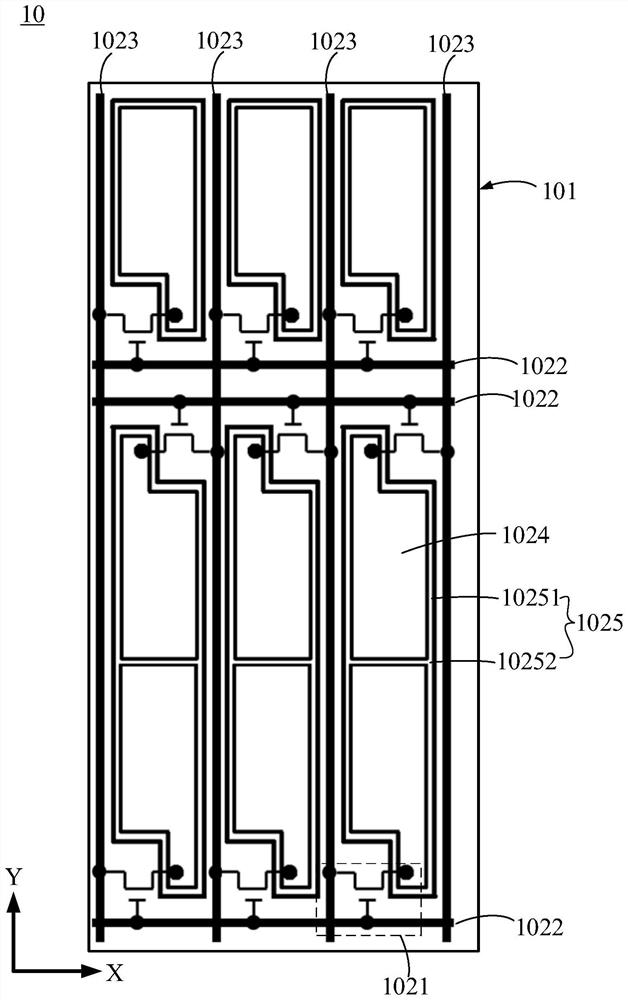

[0080] The main difference between the third embodiment and the first embodiment is that: the combination Figure 4 , Figure 5 , Figure 10 and Figure 11 As shown, in three adjacent columns of sub-pixels 102: the data lines 1023 of the sub-pixels 102 in the middle column and the data lines 1023 of the sub-pixels 102 in the adjacent columns on one side are adjacently arranged; Adjacent columns of sub-pixels 102 share a column of edge electrode strips 10251 of the common electrode 1025. For other designs, reference may be made to the content of the first embodiment, which will not be repeated here.

[0081] Wherein, the arrangement of any two adjacent columns of sub-pixels 102 is horizontally flipped to reduce design difficulty.

[0082] In the third embodiment, during the array, the sub-pixels 102 in the adjacent columns are horizontally flipped, so that the two data lines 1023 of the sub-pixels 102 in the two adjacent columns are adjacent to each other, and the sub-pixels...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com