Semiconductor device assemblies and systems with improved thermal performance and methods for making the same

A technology of semiconductors and assemblies, applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015] Certain details of several embodiments of semiconductor devices and related systems and methods are described below. Those of ordinary skill in the relevant art will recognize that suitable stages of the methods described herein may be performed at the wafer level or at the die level. Thus, depending on the context of its use, the term "substrate" may refer to a wafer-level substrate or a singulated die-level substrate. In addition, unless the context dictates otherwise, conventional semiconductor fabrication techniques may be used to form the structures disclosed herein. Materials may be deposited, for example, using chemical vapor deposition, physical vapor deposition, atomic layer deposition, electroplating, electroless plating, spin coating, and / or other suitable techniques. Similarly, material may be removed, for example, using plasma etching, wet etching, chemical mechanical planarization, or other suitable techniques.

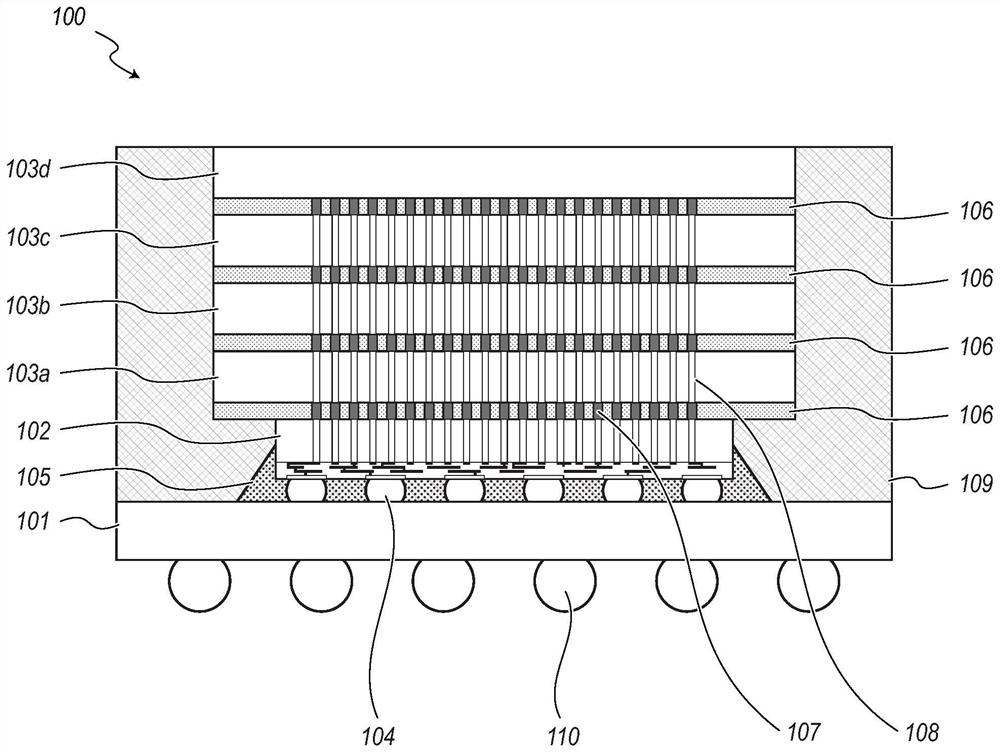

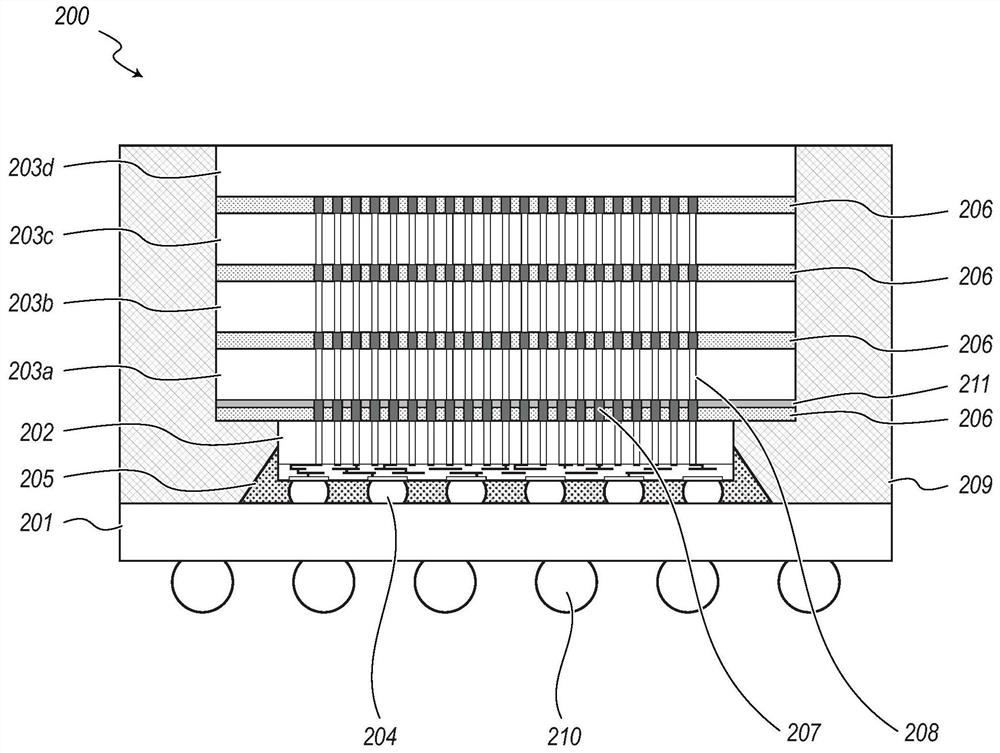

[0016] figure 1 is a simplified schemat...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com