Narrow mesa insulated gate bipolar transistor device and forming method

A technology of bipolar transistors and insulated gates, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of collector-induced barrier reduction, reduce hole concentration, eliminate CIBL effect, and enhance The effect of short-circuit resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

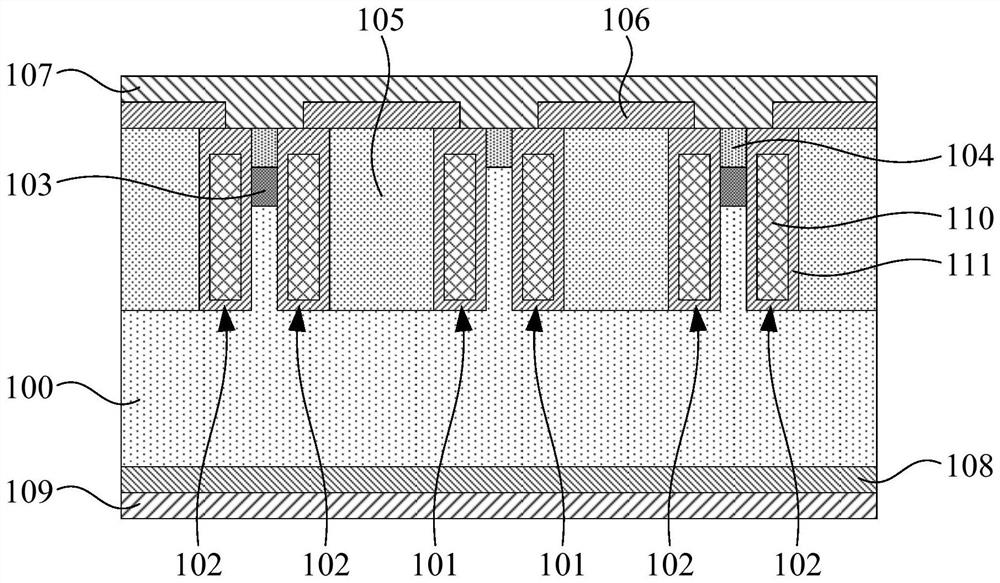

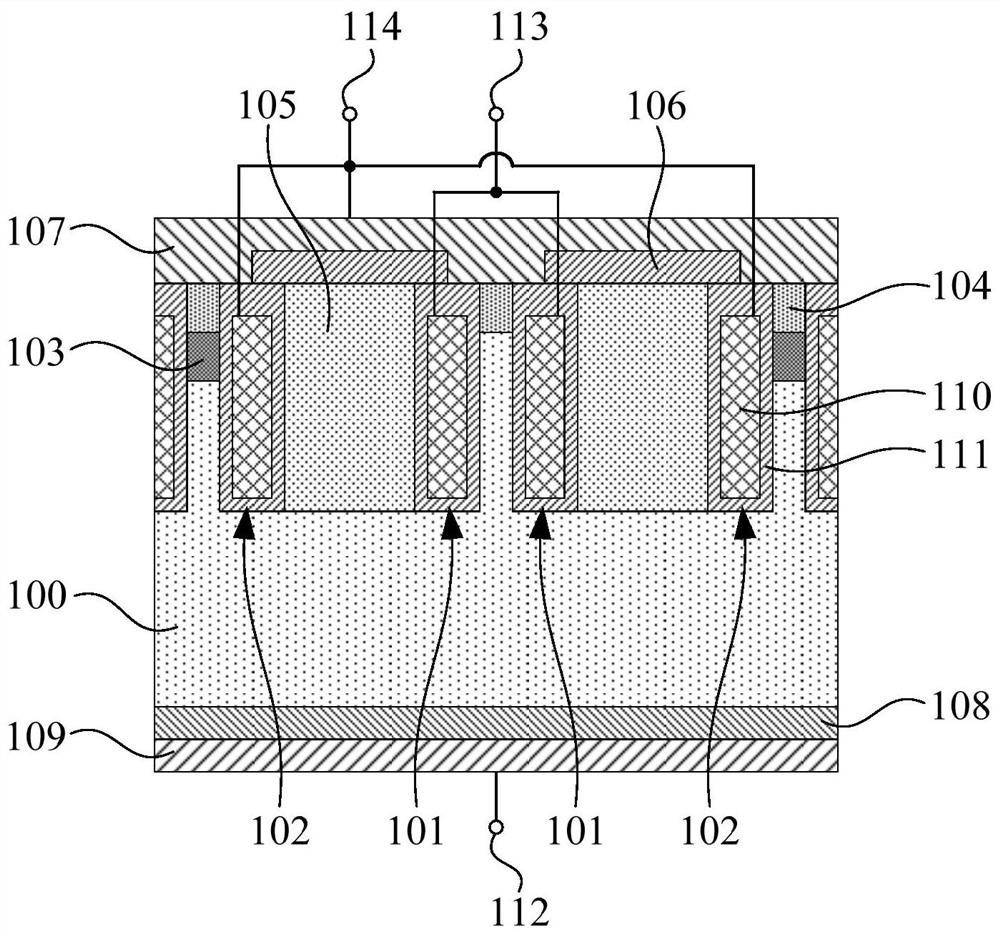

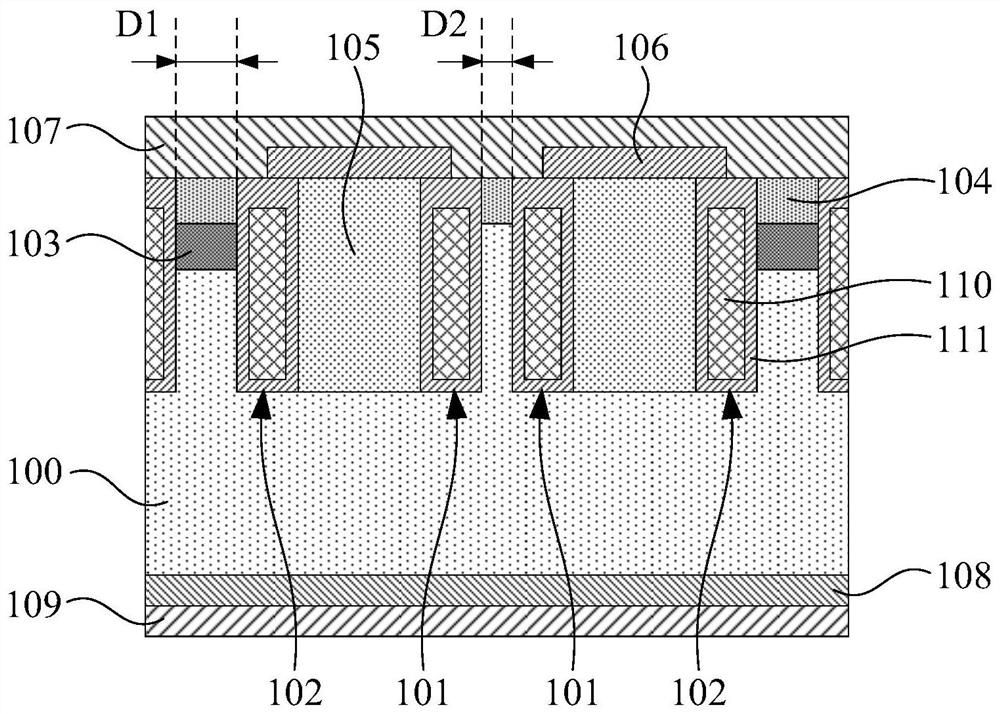

[0063] see Figure 1 to Figure 3 , this embodiment provides a narrow mesa insulated gate bipolar transistor device, which is characterized in that it includes:

[0064] a semiconductor substrate 100;

[0065] The gate trench structure 101 and the emitter trench structure 102 formed on the front surface of the semiconductor substrate 100 and arranged at intervals along the horizontal direction; the gate trench structure 101 and the emitter trench structure 102 are arranged in a direction are respectively arranged in pairs, and the paired gate trench structures 101 and the paired emitter trench structures 102 are arranged to overlap each other in the arrangement direction;

[0066] a well region 103 formed between the pair of emitter trench structures 102;

[0067] The emitter implantation region 104 formed between the paired gate trench structures 101 and between the paired emitter trench structures 102; between the paired emitter trench structures 102 In the region, the emi...

Embodiment 2

[0083] see Figure 4 to Figure 9 , the present embodiment provides a method for forming a narrow-mesa IGBT device, which is characterized in that it includes the following steps:

[0084] 1) providing a semiconductor substrate 100;

[0085] 2) Forming gate trench structures 101 and emitter trench structures 102 arranged at intervals along the horizontal direction on the front surface of the semiconductor substrate 100; the gate trench structures 101 and the emitter trench structures 102 are arranged The directions are respectively arranged in pairs, and the paired gate trench structures 101 and the paired emitter trench structures 102 are arranged to overlap each other in the arrangement direction;

[0086] 3) forming a well region 103 between the paired emitter trench structures 102;

[0087] 4) Form an emitter injection region 104 between the paired gate trench structures 101 and between the paired emitter trench structures 102; between the paired emitter trench structures...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com