Planar diode chip capable of preventing silver migration

A diode and planar technology, applied in the field of planar diode chips, can solve problems such as anode and cathode short circuits, and achieve the effects of avoiding lateral migration, facilitating chip processing, and good solderability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

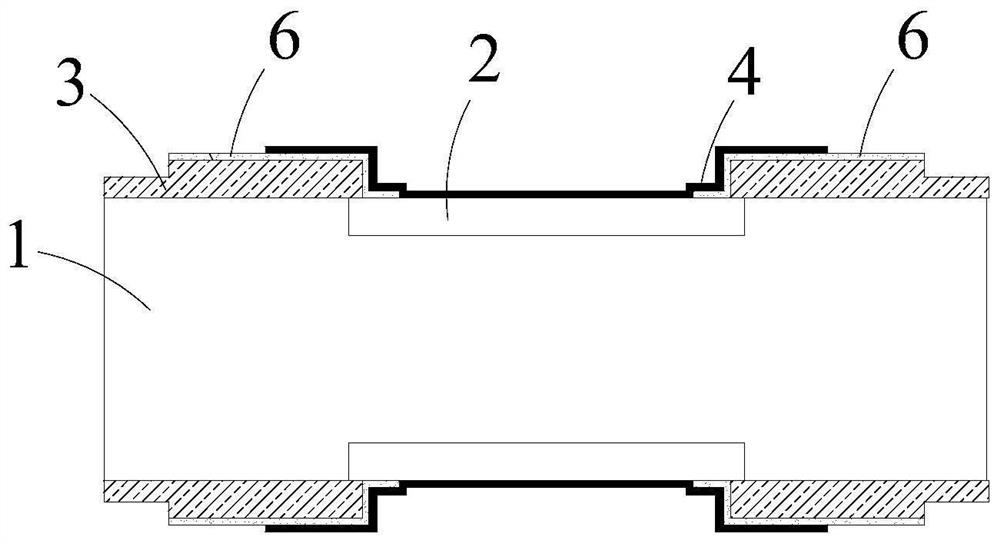

[0037] A planar diode chip, such as Figure 4 As shown, including a first semiconductor layer 1, a second semiconductor layer 2 disposed on the surface of the first semiconductor layer 1, the first semiconductor layer 1 and the second semiconductor layer 2 provide a diode structure; in the second semiconductor layer 2 The outer surface of the first semiconductor layer 1 is provided with a protective layer 3 for protecting the PN junction;

[0038] A first metal layer is provided on the surface of the second semiconductor layer 2 away from the first semiconductor layer 1 ; the first metal layer includes a soldering layer 4 , and the soldering layer 4 is located in the middle of the second semiconductor layer 2 .

[0039] The first metal layer further includes a conductive layer 5 , and the conductive layer 5 is located between the soldering layer 4 and the second semiconductor layer 2 . The conductive layer 5 is a metal that is less prone to ionization than silver. The conduc...

Embodiment 2

[0047] This embodiment is a 79mil planar TVS chip, based on the structure of Embodiment 1, an insulating layer 6 is provided between the second metal layer and the protective layer 3 . Such as Figure 5 As shown, the first semiconductor layer 1 is P-type, and the second semiconductor layer 2 and the third semiconductor layer are respectively arranged on the upper and lower sides of the first semiconductor layer 1, and both the second semiconductor layer 2 and the third semiconductor layer are N + type. The surface of the second semiconductor layer 2 is provided with a first metal layer, the surface of the third semiconductor layer is provided with a second metal layer, and the first metal layer and the third metal layer are mirror images.

[0048] side profile Figure 5 In the first metal layer on the upper side as an example, the N + The upper side of the second semiconductor layer 2 is provided with a Ti / Al conductive layer 5, and the conductive layer 5 covers the second ...

Embodiment 3

[0051] The difference between this embodiment and Embodiment 1 lies in that, in the first metal layer, the conductive layer 5 and the soldering layer 4 are arranged differently. Such as Figure 9 As shown, the first metal layer further includes a conductive layer 5 , and the conductive layer 5 is located on the surface of the second semiconductor layer 2 on the outer periphery of the soldering layer 4 . The solder layer 4 is in direct contact with the surface of the second semiconductor layer 2 .

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com