TSV multi-stress reliability test chip structure and device based on lead bonding

A chip structure and wire bonding technology, applied in the semiconductor field, can solve the problems of lack of experimental research, inability to realize multi-stress loading, etc., and achieve the effects of convenient use, scientific comprehensiveness, accuracy and reliability, and low cost.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach

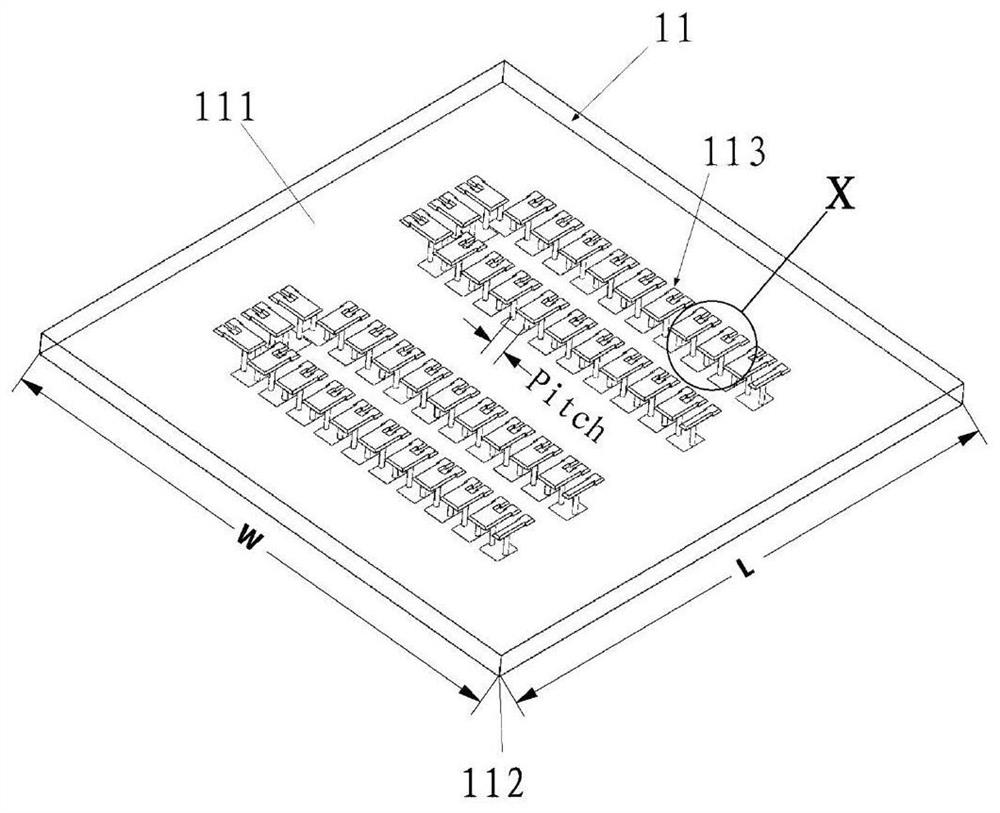

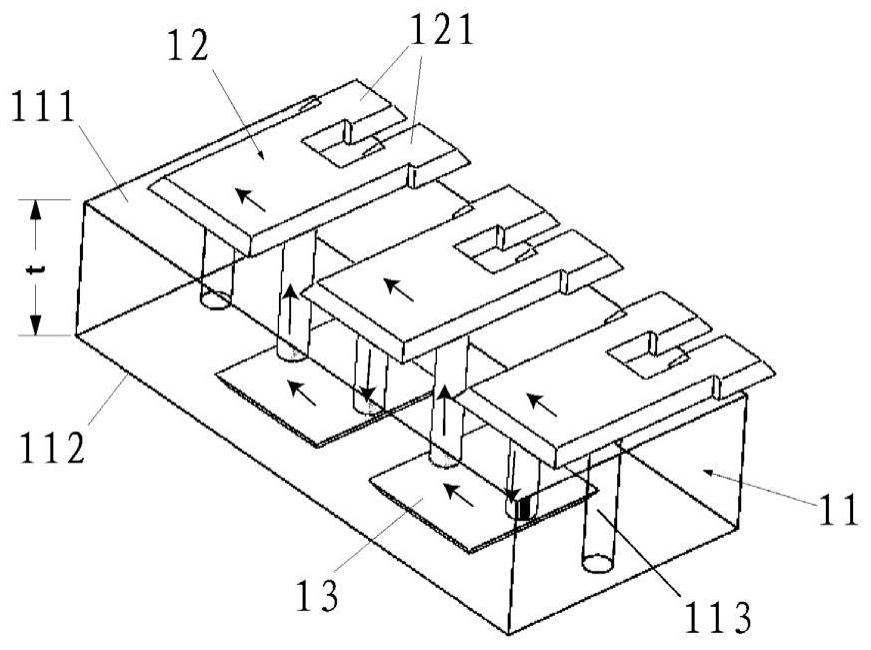

[0086] According to one embodiment of the present invention, both the chip structure with the daisy chain interconnection structure and the chip structure with the Kelvin chain interconnection structure in the present invention are taped out by designing a mask and adopting a mature process. Chips are taped out on the same wafer, and the corresponding chip die can be obtained after dicing. The outer size of the die is: L (length) × W (width) × t (thickness). In order to be able to directly load temperature and humidity to the TSV structure 113, the die is not packaged anymore. The chips are then tested and bad dies are eliminated.

[0087] The structure of the TSV multi-stress reliability test chip of the present invention can be connected to a digital acquisition system for testing after the electrodes are led out through the above-mentioned structure. Moreover, this solution realizes the reliability test in a multi-stress environment based on the above-mentioned structure. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com