Multi-channel high-speed serial LVDS data ordering method and circuit based on FPGA

A high-speed serial, multi-channel technology, applied in parallel/serial conversion, electrical components, analog-to-digital converters, etc., can solve problems such as data processing exceptions that cannot be solved

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

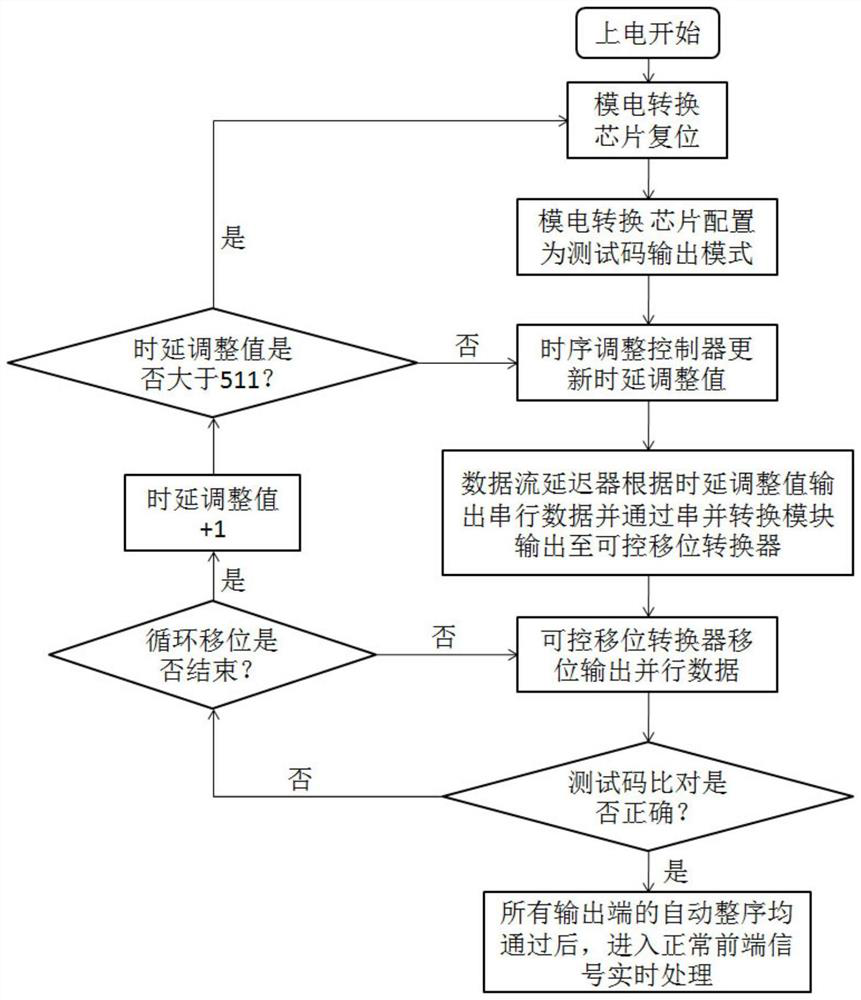

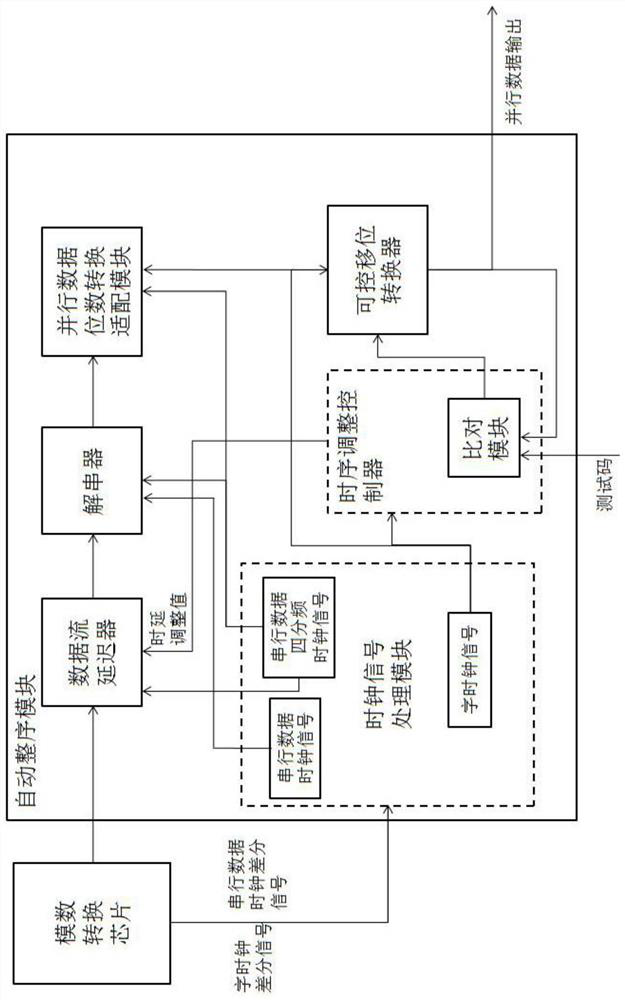

[0027] refer to Figure 1-2 , a FPGA-based multi-channel high-speed serial LVDS data ordering method, comprising the steps:

[0028] S01, the analog-to-digital conversion chip is set to a fixed test code output mode, and the serial differential data test codes output by each output port of the analog-to-digital conversion chip are respectively output to the corresponding one-to-one corresponding to each output end of the analog-to-digital conversion chip in the FPGA Automatic sequencer module; each automatic sequencer module includes at least a data stream delayer, a timing adjustment controller, a serial-to-parallel conversion module and a controllable shift converter, and the serial output from the output port of the analog-to-digital conversion chip The row differential data test code is output to the data stream delayer corresponding to the auto-sequencing module.

[0029] S02. Output the delay adjustment value of the timing adjustment controller to the data stream delaye...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com